## ALPINE LXT821

### Spread Spectrum Digital Cordless Telephone Transceiver

#### General Description

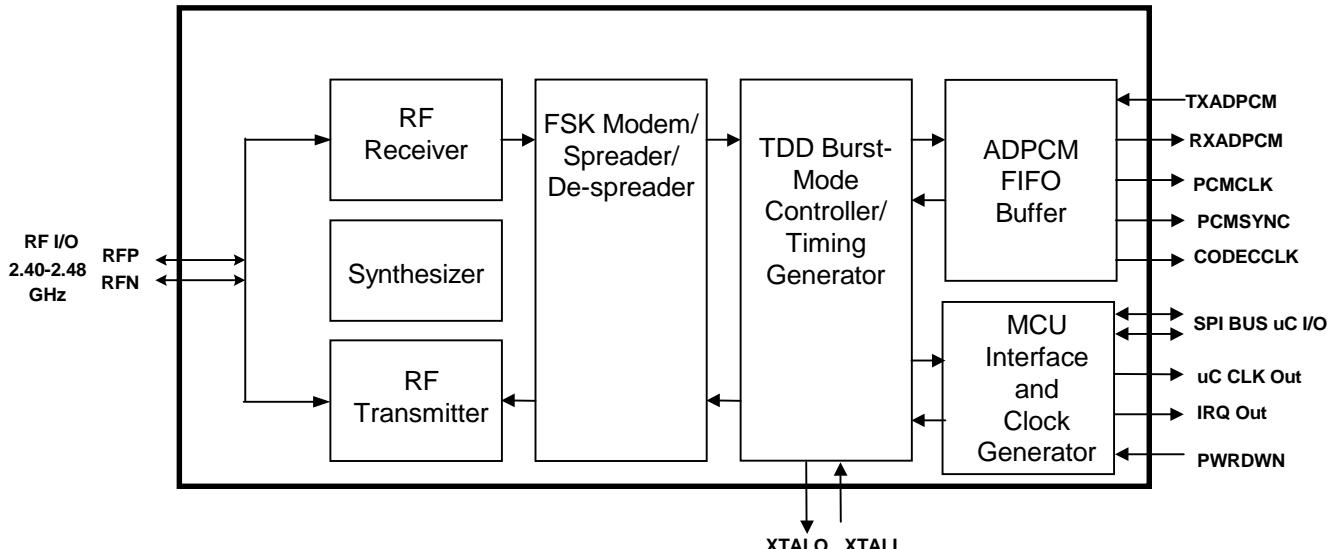

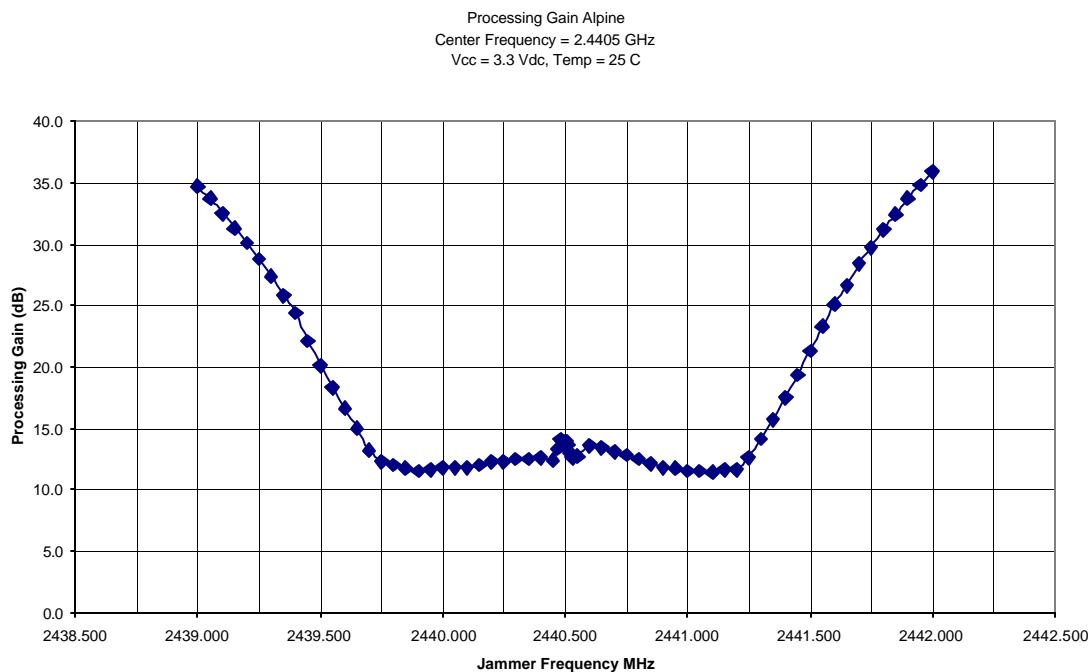

The ALPINE (LXT 821) is a single chip spread spectrum RF transceiver designed for use in 2.4 GHz Spread Spectrum Digital Cordless Telephone (SSDCT) applications. ALPINE is fully compliant with the FCC Part 15 2.4 GHz ISM band spectrum regulations.

Based on CMOS technology, ALPINE integrates a complete FM transceiver suitable for direct sequence spread spectrum applications. ALPINE includes a 2.4 GHz synthesizer, transmit power amplifier, receive low noise amplifier, antenna switch, channel select filtering, FSK demodulator, and a complete TDD burst-mode controller with forward error correction in a single integrated circuit.

ALPINE can be combined with an ADPCM CODEC and a micro-controller to create a complete SSDCT terminal. No other ICs are required.

The LXT 821 performs all multiplexing / de-multiplexing and spreading / de-spreading functions required to transmit a 32k b/s ADPCM voice signal and 4k b/s data channel over a 2.4 GHz radio link.

#### Applications

- Spread Spectrum Digital Cordless Telephones

- Wireless security and monitoring transceivers

- Wireless Spread Spectrum Data/Voice Transceivers

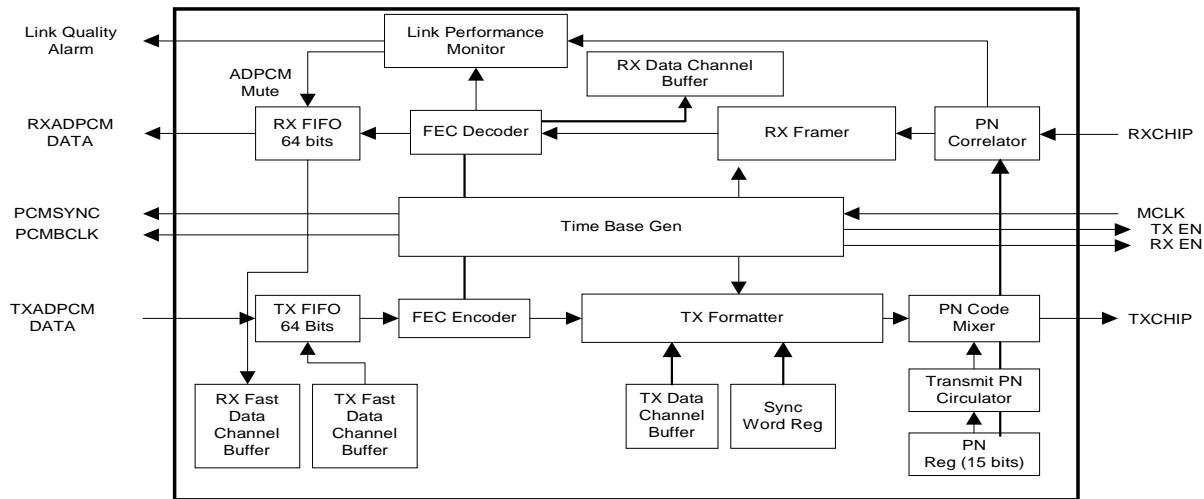

#### ALPINE Block Diagram

**ALPINE LXT821**

*Spread Spectrum Digital Cordless Telephone Transceiver*

### 1. Revision History

| Revision Number | Date     | Originator                            | Revision description                                                                                                                            |

|-----------------|----------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0             | 11/18/99 | C. Nilson                             | Initial Revision from LXT 820 Rev 1.4 and LXT 801 Rev 2.1                                                                                       |

| 1.1             | 11/30/99 | C. Nilson                             | Revised pin names and descriptions to correspond to LXT810                                                                                      |

| 2.0             | 4/30/00  | D. Jones                              | Update to B1 Revision, add sections on Pin Signal Muxing and Channel Coding                                                                     |

| 3.0             | 6/22/00  | D. Jones<br>E. Dukatz<br>A. Dickinson | Major Revision of Register Descriptions, Pin Signal Descriptions, added Register Descriptions for new Auto-mute control via Window Path Metric. |

| 3.1             | 6/25/00  | D. Jones                              | Add description of IRQ timing in Slave search mode<br>Update A1 to B1 changes list                                                              |

| 3.2             | 6/28/00  | L. Plouvier                           | Add full registers description, update definition, defaults and recommendations                                                                 |

| 4.0             | 9/21/00  | E. Dukatz                             | Based on Rev 4.1 Design Specification                                                                                                           |

| 4.1             | 9/25/00  | E. Dukatz                             | Corrected Crystal Specification and FRMCTRL register description                                                                                |

| 4.2             | 10/14/00 | E. Dukatz                             | Revised Specifications                                                                                                                          |

| 4.3             | 11/3/00  | E. Dukatz                             | Changed lowest channel frequency and frequency deviation specification to provide margin on FCC spec.                                           |

|                 |          |                                       |                                                                                                                                                 |

# ALPINE LXT821

## Spread Spectrum Digital Cordless Telephone Transceiver

### 2. Table of Contents:

|      |                                                                                                                |    |

|------|----------------------------------------------------------------------------------------------------------------|----|

| 1.   | Revision History .....                                                                                         | 2  |

| 2.   | Table of Contents: .....                                                                                       | 3  |

| 3.   | List of Figures.....                                                                                           | 5  |

| 4.   | List of Tables .....                                                                                           | 5  |

| 5.   | Introduction .....                                                                                             | 6  |

| 5.1  | The ALPINE Spread Spectrum Digital Cordless Telephone RF Transceiver .....                                     | 6  |

| 5.2  | Operation Overview.....                                                                                        | 6  |

| 6.   | Pin Assignments and Signal Descriptions .....                                                                  | 9  |

| 6.1  | Package Description.....                                                                                       | 9  |

| 6.2  | RF Interface Pins .....                                                                                        | 10 |

| 6.3  | ADPCM Interface Pins .....                                                                                     | 11 |

| 6.4  | SPI bus Micro-controller Interface .....                                                                       | 11 |

| 6.5  | Miscellaneous Pin Descriptions .....                                                                           | 12 |

| 6.6  | Power Supply Pins .....                                                                                        | 13 |

| 7.   | Interfaces and Functions.....                                                                                  | 13 |

| 7.1  | RF Interface Description .....                                                                                 | 14 |

| 7.2  | Channel Coding and Direct Sequence Spreading.....                                                              | 19 |

| 7.3  | ADPCM CODEC Interface .....                                                                                    | 21 |

| 7.4  | Micro-Controller Interface Description.....                                                                    | 23 |

| 7.5  | Spread Spectrum Processor/Burst-mode Controller Description .....                                              | 33 |

| 8.   | ALPINE Register Map.....                                                                                       | 41 |

| 9.   | Alpine Register Description .....                                                                              | 43 |

| 9.1  | PN Code Word 1 – Address 00 hex.....                                                                           | 43 |

| 9.2  | PN Code Word 2 – Address 01 hex.....                                                                           | 43 |

| 9.3  | Preamble – Low and High – Address 02 and 03 hex.....                                                           | 43 |

| 9.4  | Sync Word – Address 04 hex, <b>Recommended: F6</b> .....                                                       | 44 |

| 9.5  | Alpine Control – Address 05 hex .....                                                                          | 44 |

| 9.6  | TX Data Channel – Address 06 hex.....                                                                          | 45 |

| 9.7  | RX Data Channel – Address 07 hex.....                                                                          | 45 |

| 9.8  | Fast Data Channel Control/Status – Address 08 hex .....                                                        | 45 |

| 9.9  | TX Fast Data Channel Buffer – Address 09 hex.....                                                              | 46 |

| 9.10 | RX Fast Data Channel Buffer – Address A hex.....                                                               | 46 |

| 9.11 | TX Frame Format Control – Address 0B hex.....                                                                  | 47 |

| 9.12 | RX Frame Format Control – Address 0C hex, <b>Recommended: 80</b> .....                                         | 48 |

| 9.13 | RX Correlator Control – Address 0D hex.....                                                                    | 48 |

| 9.14 | RX Framer Control – Address 0E hex, <b>Recommended: 38</b> .....                                               | 49 |

| 9.15 | Clock Generator Control – Address 0F hex, <b>Recommended: 18</b> .....                                         | 51 |

| 9.16 | Auto-mute Control – Address 10 hex <b>Recommended: 9F</b> .....                                                | 52 |

| 9.17 | Link Quality Alarm Threshold – Address 11 hex, <b>Recommended: 12</b> .....                                    | 52 |

| 9.18 | Link Quality Monitor Control – Address 12 hex.....                                                             | 53 |

| 9.19 | Receiver Status – Address 13 hex .....                                                                         | 53 |

| 9.20 | Interrupt Timing Control – Address 14 hex <b>Recommended: 02</b> .....                                         | 54 |

| 9.21 | Power Down Control – Address 16 hex.....                                                                       | 55 |

| 9.22 | RX Frame Sync – Address 18 hex.....                                                                            | 55 |

| 9.23 | RX Frame Search – Address 19 hex.....                                                                          | 55 |

| 9.24 | Path Metric Window Size – Address 1A hex, <b>Recommended: 10</b> .....                                         | 56 |

| 9.25 | Drive Strength Control – Address 2D hex,.....                                                                  | 56 |

| 9.26 | Chip Version – Address 2F hex.....                                                                             | 56 |

| 9.27 | Receive Gain Indicator – Address 30hex - Read Only .....                                                       | 57 |

| 9.28 | Manual Power Control, TXCHIP, and Clock Drive Strength – Address 33 hex -Def: 78, <b>Recommended: 40</b> ..... | 58 |

| 9.29 | Channel Select Registers – Address 40 to 42 hex – Defaults: 04, 0E and 04 (Channel @ 2.4405 GHz).....          | 59 |

| 9.30 | Transmit Power Adjust – Address 43hex – Default: 0F (1.5 MHz PA ramp on and 20 dBm).....                       | 61 |

| 9.31 | PLLSWEN TWI Register - Address 53 hex – Default: 00 .....                                                      | 62 |

| 9.32 | MNBWEN TWI Register - Address 57 hex – Default: 06 <b>Recommended: 04</b> .....                                | 62 |

| 9.33 | CHPMPHIEN TWI Register - Address 5B hex – Default: 07 .....                                                    | 63 |

| 9.34 | CHPMPLOEN TWI Register - Address 5C hex – Default: 01 .....                                                    | 63 |

| 10.  | Alpine A1 vs. B1 Differences .....                                                                             | 64 |

| 11.  | RF System Specifications:.....                                                                                 | 65 |

| 12.  | Electrical Specifications .....                                                                                | 67 |

**ALPINE LXT821**

*Spread Spectrum Digital Cordless Telephone Transceiver*

|      |                                              |    |

|------|----------------------------------------------|----|

| 12.1 | Absolute Maximum Ratings .....               | 67 |

| 12.2 | Recommended Operating Conditions.....        | 67 |

| 12.3 | Digital I/O Electrical Characteristics ..... | 67 |

| 13.  | Contact Information:.....                    | 68 |

# ALPINE LXT821

## Spread Spectrum Digital Cordless Telephone Transceiver

### 3. List of Figures

|                                                                                         |    |

|-----------------------------------------------------------------------------------------|----|

| Figure 1: Low Cost RF / Baseband Configuration .....                                    | 6  |

| Figure 2: ALPINE TDD Frame Format.....                                                  | 8  |

| Figure 3: RF Input and Output .....                                                     | 14 |

| Figure 4: Synthesizer Test Circuit.....                                                 | 15 |

| Figure 5: Crystal Oscillator test Circuit .....                                         | 18 |

| Figure 6, Channel Coding and Spreading.....                                             | 19 |

| Figure 7, Data Scrambler LFSR .....                                                     | 20 |

| Figure 8, Alpine Convolutional Encoder .....                                            | 20 |

| Figure 9 ALPINE / CODEC Interface Connections .....                                     | 21 |

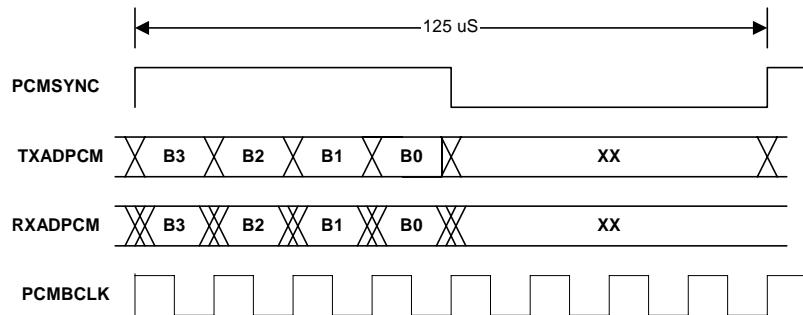

| Figure 10: ADPCM Interface Timing Diagram Mode 0.....                                   | 22 |

| Figure 11: ADPCM Interface Timing Diagram Mode 1.....                                   | 22 |

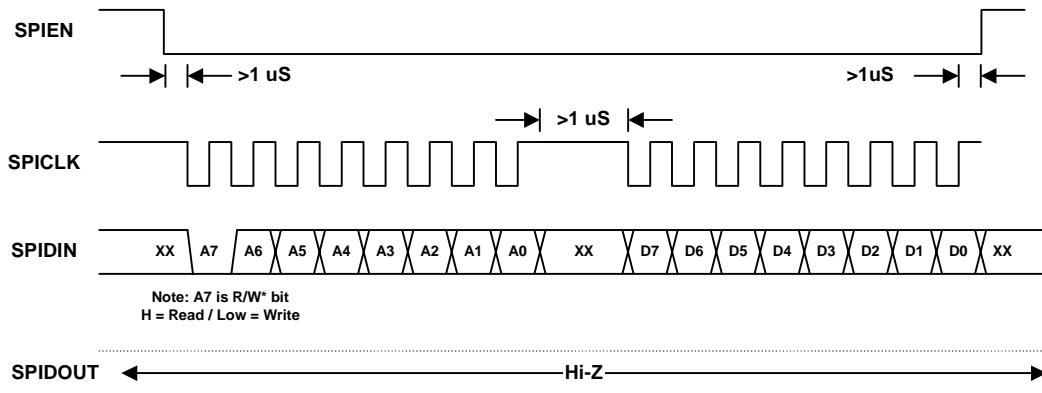

| Figure 12: SPI Bus Write Operation Timing Diagram.....                                  | 24 |

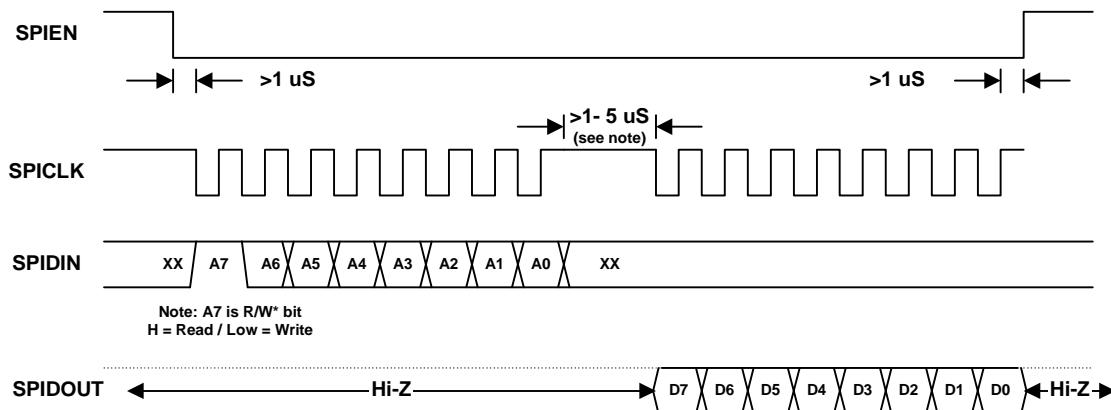

| Figure 13: SPI Bus Read Operation Timing Diagram.....                                   | 25 |

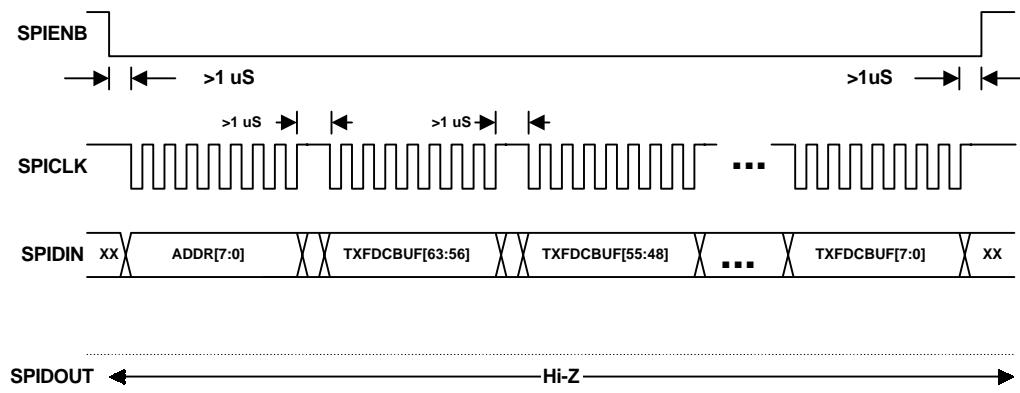

| Figure 14: TX Fast Data Channel Write Operation Timing Diagram .....                    | 26 |

| Figure 15: RX/TX Fast Data Channel Read Operation Timing Diagram .....                  | 27 |

| Figure 16- IRQ Interrupt Timing .....                                                   | 29 |

| Figure 17: Power Up Reset Timing Vs Power Supply Voltage .....                          | 30 |

| Figure 18: Reset Timing .....                                                           | 31 |

| Figure 19 - Functional Block diagram of the Spread Spectrum Burst Mode Controller ..... | 34 |

| Figure 20 TDD Frame Format of BMC (normal mode) .....                                   | 35 |

| Figure 21 TDD Frame Format of BMC (short packet mode) .....                             | 36 |

### 4. List of Tables

|                                                                                  |    |

|----------------------------------------------------------------------------------|----|

| Table 1 : RF Interface Pin Descriptions.....                                     | 10 |

| Table 2: ALPINE ADPCM Interface Pin Descriptions .....                           | 11 |

| Table 3: Micro-controller Interface Pin Descriptions .....                       | 11 |

| Table 4 : Miscellaneous Pin Description .....                                    | 12 |

| Table 5: Power Supply Pin Descriptions.....                                      | 13 |

| Table 6 Synthesizer Specifications.....                                          | 15 |

| Table 7: Crystal Oscillator Specifications.....                                  | 17 |

| Table 8 - Standby Oscillator Component Values .....                              | 33 |

| Table 9: Alpine Register Map .....                                               | 42 |

| Table 10: Loss of Sync Threshold, Link Quality Monitor > 20.....                 | 49 |

| Table 11: Sync Declaration Threshold .....                                       | 50 |

| Table 12: Receive Gain Indicator Bit Definitions .....                           | 57 |

| Table 13: Receive Gain Given Register State .....                                | 57 |

| Table 14: Power Control Functionality .....                                      | 58 |

| Table 15: Channel Select register Set.....                                       | 59 |

| Table 16 Address 40h, LSB's of the A count setting, bit definitions.....         | 59 |

| Table 17 Address 41h, LSB's of the M count setting, bit definitions.....         | 59 |

| Table 18 Address 42h, MSB'S of both A and M count settings, bit definitions..... | 59 |

| Table 19: Valid A and M Count Values .....                                       | 60 |

| Table 20 Transmit Power Set Bit Definitions .....                                | 61 |

| Table 21: PLL Switch Time Duration .....                                         | 62 |

| Table 22 ALPINE RF System Specification Sheet .....                              | 66 |

# ALPINE LXT821

## Spread Spectrum Digital Cordless Telephone Transceiver

### 5. Introduction

#### 5.1 The ALPINE Spread Spectrum Digital Cordless Telephone RF Transceiver

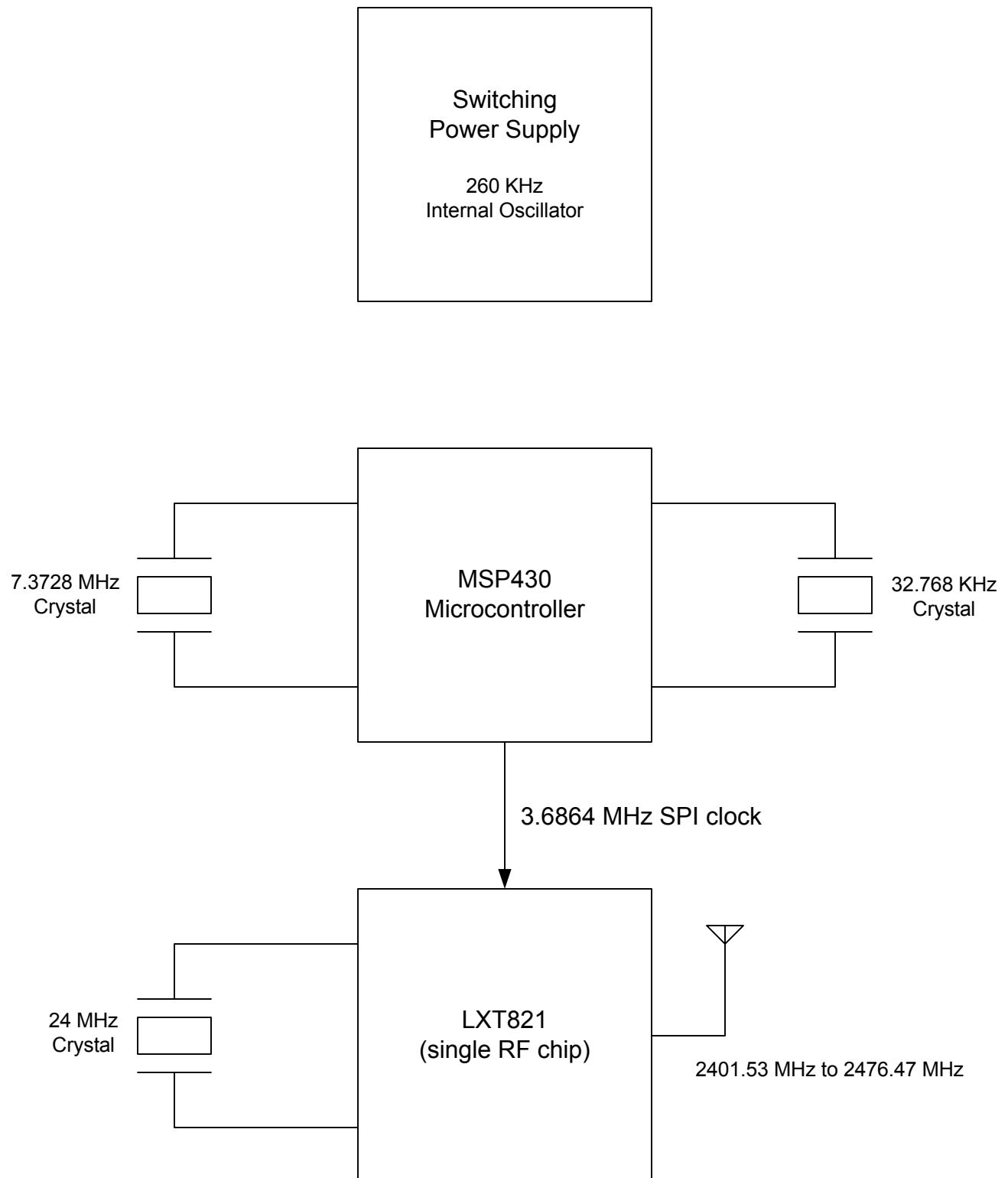

ALPINE is a fully integrated spread-spectrum capable FSK RF Transceiver within a single integrated circuit, which has been optimized for 2.4 GHz spread spectrum digital cordless telephone applications.

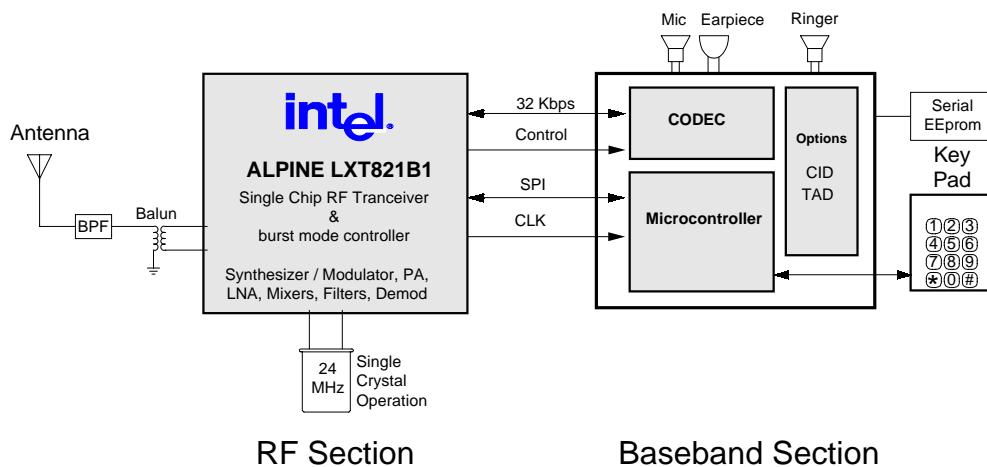

A three-chip, single crystal SSDCT terminal can be implemented by combining ALPINE with an ADPCM CODEC, and a standard “off the shelf” micro-controller.

##### 5.1.1

Figure 1: Low Cost RF / Baseband Configuration

### 5.2 Operation Overview

ALPINE provides all of the necessary active components for a complete 2.4 GHz ISM band FSK transceiver. The ALPINE burst-mode controller (BMC) block performs all spreading / de-spreading, framing / formatting, and time-division duplex (TDD) control required to implement a 2.4 GHz spread spectrum radio suitable for Spread Spectrum Digital Cordless Telephone applications (SSDCT). When combined with an external ADPCM voice codec and micro-controller (MCU), the LXT821 forms a complete SSDCT terminal (base or handset).

ALPINE performs virtually all RF link layer processing required for SSDCT use. Once initialized, the ALPINE is self-synchronizing, and MCU intervention is only required for monitoring RF link performance, RF channel selection and transmit output power setting.

A complete handset can be realized with three integrated circuits and fewer than 30 discrete components, such as, a ceramic 2.4 GHz band pass filter, balun, capacitors, inductors and resistors. No other active components are required.

## ALPINE LXT821

### Spread Spectrum Digital Cordless Telephone Transceiver

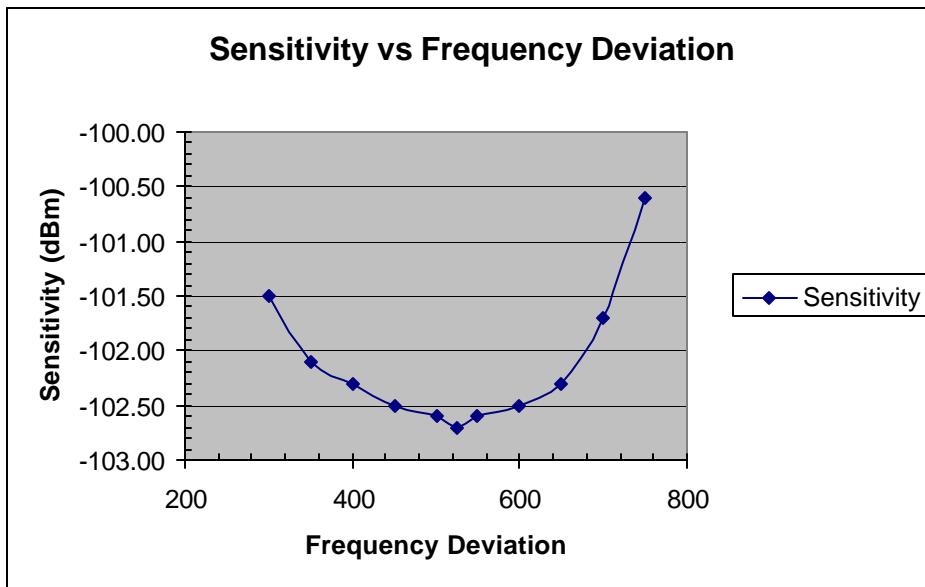

#### 5.2.1 Transmit Operation

In the transmit direction, the LXT821 combines a 32k b/s ADPCM data input with a 4k b/s data channel input, encapsulates the data in a TDD frame with a preamble and sync word and uses direct sequence spreading to create a binary TX chipping sequence for output to the RF transmitter block. TXCHIP is a digitally spread 1.5 Mchip/Sec signal that is then filtered and level shifted within ALPINE and directly modulates the 2.4 GHz synthesizer. The 2.4 GHz FSK modulated RF signal is then passed on to the internal power amplifier. The power amplifier is capable of transmitting at power levels of +20 dBm, +14 dBm, +8 dBm and +2 dBm.

The power amplifier is automatically disabled as long as the synthesizer is out of lock. This can be the case for a short duration of time (~ 2 mS) upon power up and during RF channel changes. The transmit power amplifier shares a common I/O port with the receive low noise amplifier. Due to the time division duplex operation, the transmitter and receiver are never on at the same time. Because of this, an external antenna switch is **NOT** required.

#### 5.2.2 Receive Operation

For reception, the 2.4 GHz Spread FSK Receive Signal is first low noise amplified and then down converted into a baseband I and Q signal format. The baseband I and Q signals are then AGC amplified, offset cancelled, and filtered for channel selection purposes. The filtered I and Q baseband signals are then A/D converted and FSK demodulated. The BMC block accepts the resulting binary 1.5Mchip/s output, which is then de-spread and de-multiplexed into the 32k b/s ADPCM voice data and 4k b/s data channel signals.

The LXT821 provides radio link diagnostic information to the MCU for active link management capabilities (adaptive power control and channel hopping algorithms), including a Link Quality Alarm output (LQA). The LQA is available both in a register bit and at a dedicated pin making it suitable for antenna diversity applications.

#### 5.2.3 Transceiver Control

The automatic gain control (AGC) section of the receiver supplies a Receive Signal Strength Indicator in the form of receiver gain to the MCU via the 4-wire serial peripheral interface (SPI) bus. The receiver gain data is valid for input levels from -96 dBm to -28 dBm. receiver gain changes in increments of 6dB.

The receiver gain information is useful for far end adaptive transmit power control. In addition, when the receiver gain data from ALPINE is combined with the Link Quality information, in-band interference can be determined. Channel selection can then be based on a combination of receive signal level and interference.

Channel selection is accomplished by programming the 2.4 GHz synthesizer within ALPINE via the 4 wire SPI Bus by the external micro-controller.

Finally, ALPINE can be powered down and will draw less than 100 uA of current. Power down is accomplished by writing to the appropriate SPI control register, or by driving the external PWRDNP pin.

## **ALPINE LXT821**

### *Spread Spectrum Digital Cordless Telephone Transceiver*

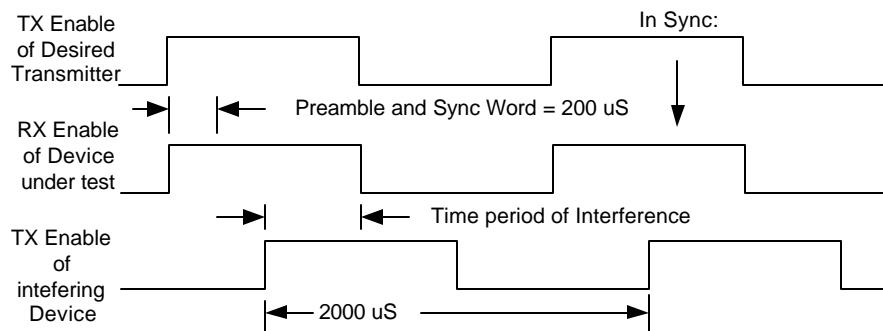

#### **5.2.4 Time Division Duplex**

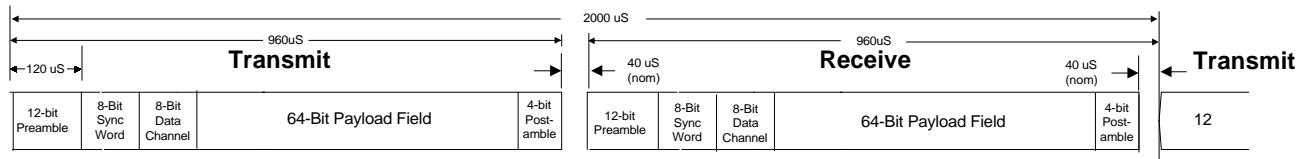

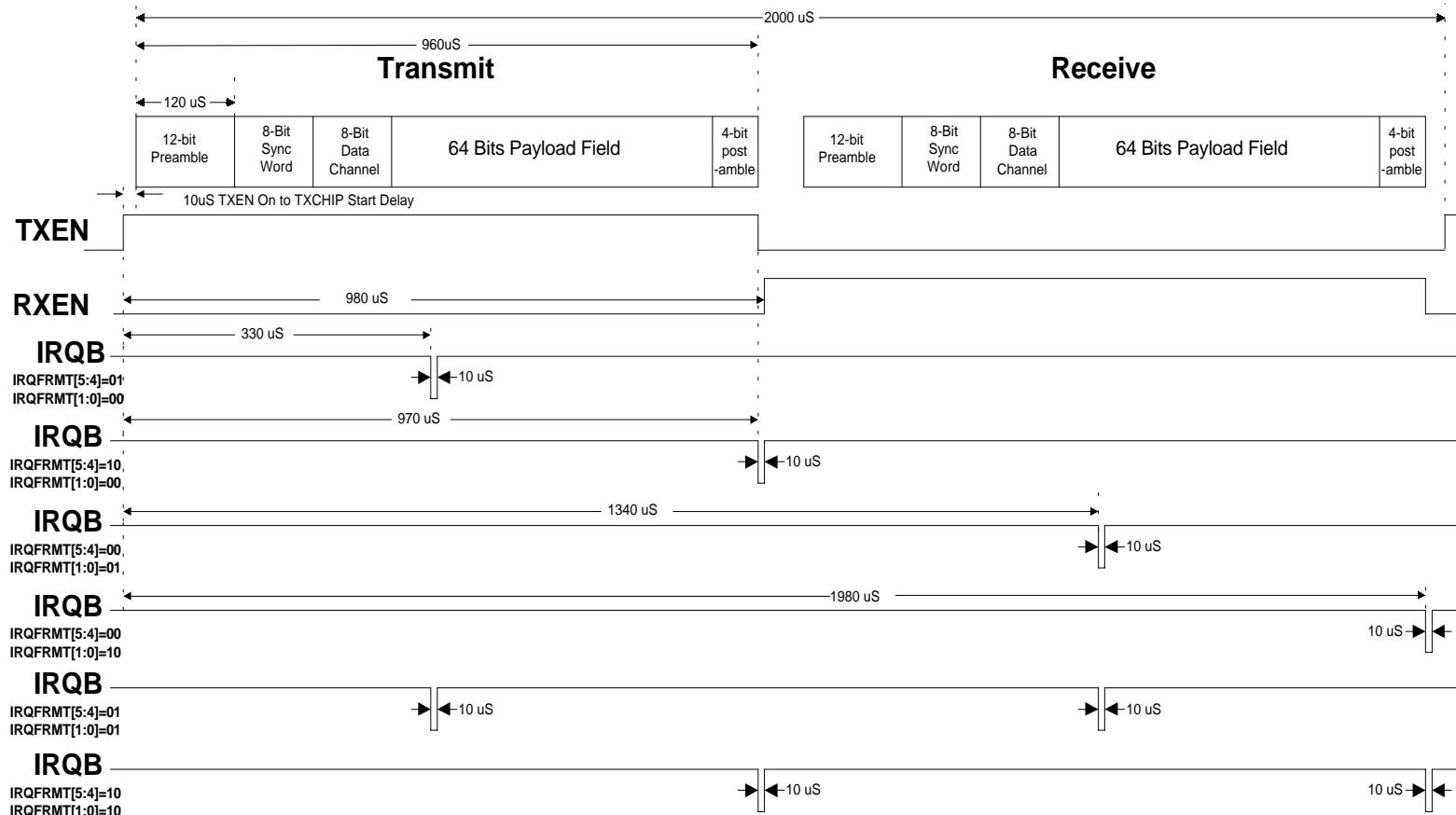

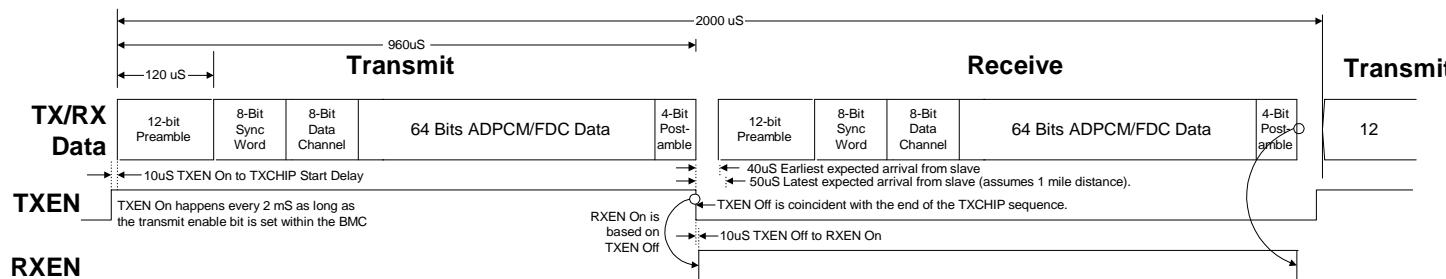

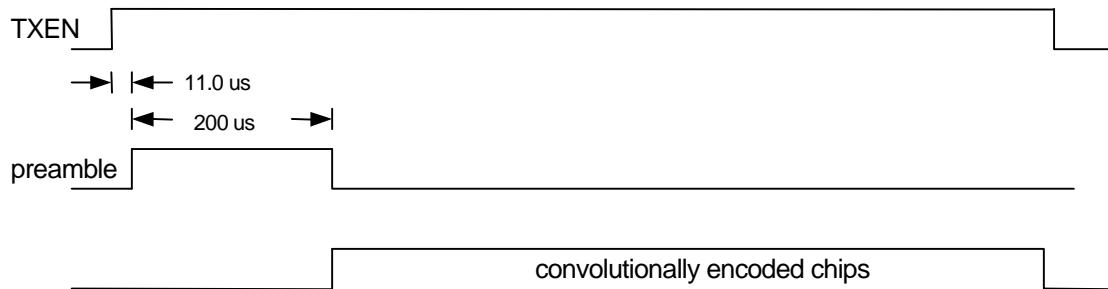

ALPINE uses the time division duplex (TDD) frame format shown in Figure 2.

The TDD frame is 2mS in length, and is composed of two symmetrical 960 uS TX and RX subframes. Each subframe contains 96 bits of 10uS duration, with 40 uS guard times between both TX and RX subframes.

Each subframe consists of the following four fields:

- A 12-bit Preamble field

- An 8-bit Sync Word

- An 8-bit Data Channel field

- A 64-bit Payload

- A 4-bit Post-amble

Both the 8-bit Sync Word and 8-bit Data Channel are programmable via the MCU interface. In addition, the 64-bit payload can be filled either with ADPCM voice data, or can be used by the host MCU as a fast data channel between base and handset. See the register descriptions that follow for details.

**Figure 2: ALPINE TDD Frame Format**

# ALPINE LXT821

## Spread Spectrum Digital Cordless Telephone Transceiver

### 6. Pin Assignments and Signal Descriptions

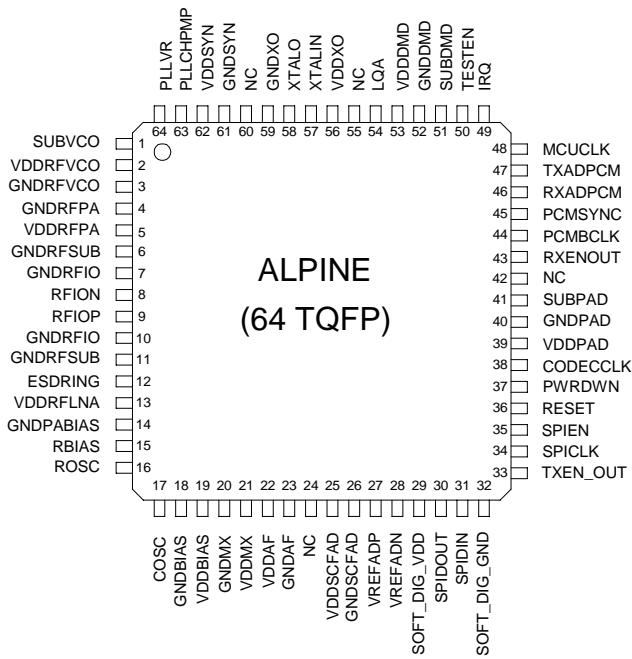

#### 6.1 Package Description

ALPINE utilizes a 64 pin TQFP with package dimensions of 10 x 10 x 1.4 mm<sup>3</sup>

# ALPINE LXT821

## Spread Spectrum Digital Cordless Telephone Transceiver

### 6.2 RF Interface Pins

Table 1 : RF Interface Pin Descriptions

| Pin # | Name      | I/O | Description                                                                                                                                                                                      |

|-------|-----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8     | RFION     | I/O | <b>Balanced RF Input and Output Negative Side</b><br>Used in conjunction with RFIOP to create a balanced RF I/O port.                                                                            |

| 9     | RFIOP     | I/O | <b>Balanced RF Input and Output Positive Side</b><br>Used in conjunction with RFION to create a balanced RF I/O port.                                                                            |

| 33    | TXEN_OUT  | O   | <b>Can be used by external circuitry.</b> When high this pin indicates that the transmitter is enabled. Normally Disconnected.                                                                   |

| 43    | RXENOUT   | O   | <b>RXENOUT:</b> When high this pin indicates that the receiver is enabled.                                                                                                                       |

| 54    | LQA       | O   | <b>Link Quality Alarm:</b><br>The Link Quality Alarm indicates when the correlator error rate exceeds a programmed threshold. The threshold is programmed in register 0x11.                      |

| 63    | PLLCHPMPP | NA  | <b>Phase Locked Loop Charge Pump:</b><br>The PLL loop filter components connect between PLLRC and PLLVR. Charge pump current drives the external loop filter on this pin.                        |

| 64    | PLLVR     | NA  | <b>Phase Locked Loop Varactor Reference Voltage:</b><br>A regulated varactor reference voltage is used to increase the VCO PSRR. The PLL loop filter components connect between PLLRC and PLLVR. |

# ALPINE LXT821

## Spread Spectrum Digital Cordless Telephone Transceiver

### 6.3 ADPCM Interface Pins

Table 2: ALPINE ADPCM Interface Pin Descriptions

| Pin # | Name     | I/O | Description                                                                                                                                                                           |

|-------|----------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 47    | TXADPCM  | I   | <b>Transmit ADPCM Data: (TXADPCM)</b><br>TXADPCM receives the 32k b/s ADPCM data output signal of an external ADPCM CODEC IC.                                                         |

| 46    | RXADPCM  | O   | <b>Receive ADPCM Data: (RXADPCM)</b><br>RXADPCM drives the 32k b/s ADPCM data input line of an external ADPCM CODEC IC.                                                               |

| 38    | CODECCLK | O   | <b>CODEC Master Clock: (CODECCLK)</b><br>The CODEC clock can be programmed to either 19.2 MHz or 24.0 MHz to drive the master clock input to an external ADPCM CODEC IC.              |

| 44    | PCMBCLK  | O   | <b>PCM Bit Clock: (PCMBCLK)</b><br>PCM Clock operates at 32k b/s or 64k b/s and is used to clock both the transmit and receive PCM data to an external ADPCM CODEC IC                 |

| 45    | PCMSYNC  | O   | <b>PCM Synchronization Clock: (PCMSYNC)</b><br>PCMSYNC operates at 8 kHz and is used to synchronize the MSB of both transmit and receive ADPCM signals to an external ADPCM CODEC IC. |

### 6.4 SPI bus Micro-controller Interface

Table 3: Micro-controller Interface Pin Descriptions

| Pin # | Name    | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------|---------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30    | SPIDOUT | O   | <b>SPIDOUT: SPI Data Out</b><br>Data Output for byte-wise data transmitted serially to the MCU, MSB first. Data transitions are on the falling edge of SPICLKIN and the data is sampled by the MCU on the rising edge of SPICLKIN.                                                                                                                                                                                                               |

| 31    | SPIDIN  | I   | <b>SPIDIN: SPI Data Input</b><br>Data input for byte-wise data transmitted serially from the MCU, MSB first. Data is sampled by the BMC on the rising edge of SPICLKIN.                                                                                                                                                                                                                                                                          |

| 34    | SPICLK  | I   | <b>SPICLKIN: SPI Clock Input</b><br>Serial clock to synchronize the data movement both in and out of the BMC.                                                                                                                                                                                                                                                                                                                                    |

| 35    | SPIEN   | I   | <b>SPIEN: SPI Bus Enable - Active Low</b><br>The SPIEN line is used to select ALPINE as a slave device for data transactions. It must be low prior to the beginning of a transaction and must stay low for the duration of the transaction.                                                                                                                                                                                                      |

| 48    | MCUCLK  | O   | <b>MCUCLK: Micro-Controller Clock</b><br>The micro-controller clock frequency can be programmed to various operating frequencies, 100 kHz, 2 MHz, 4 MHz, 6 MHz, 12 MHz. In addition when the IC is powered down the MCUCLK is placed in a low speed mode (100 kHz or 200 kHz) to allow the external micro-controller to draw less power. When in the low power mode the frequency is determined by ROSC and COSC on pins 16 and 17 respectively. |

| 49    | IRQ     | O   | <b>IRQ: Interrupt Request:</b> The interrupt is generated on various edges of the transmit and receive frame as determined by register 0x14. When the interrupt is not selected the pin is used to monitor the state of the synthesizer unit cap controller for test purposes.                                                                                                                                                                   |

# ALPINE LXT821

## Spread Spectrum Digital Cordless Telephone Transceiver

### 6.5 Miscellaneous Pin Descriptions

Table 4 : Miscellaneous Pin Description

| Pin # | Name    | I/O | Description                                                                                                                                                                                                                                                                                                   |

|-------|---------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 37    | PWRDWN  | I   | <p><b>PWRDWN: Power Down: ( Active Hi )</b><br/> This can be driven from the CODEC or from an external micro-controller.</p> <p><b>Errata:</b> The power down pin does not turn off the BMC section in the LXT821A1. In both the LXT821A1 and LXT821B1, it does not reset the receiver state machines.</p>    |

| 36    | RESET   | I   | <p><b>RESET: ( Active Low )</b><br/> Resets all registers to known states.</p>                                                                                                                                                                                                                                |

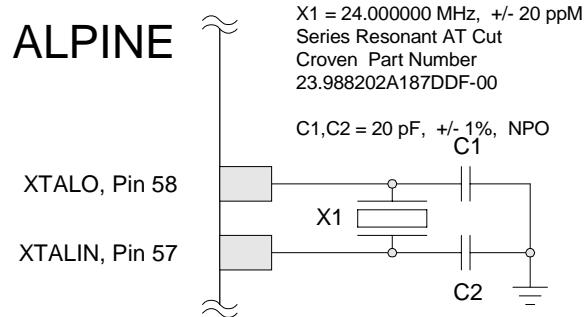

| 57    | XTALIN  | I   | <p><b>Crystal Connection Input:</b><br/> One terminal of a +/- 30 PPM AT Cut 24 MHz crystal is connected here. A 20 pF capacitor is also connected from this pin to ground for proper phasing.<br/> It is also possible to AC couple an external 24 MHz Clock of 0.2 to 2 Vp-p to this input.</p>             |

| 58    | XTALO   | O   | <p><b>Crystal Connection Output:</b><br/> One terminal of a +/- 30 PPM AT Cut 24 MHz crystal is connected here. A 20 pF capacitor is also connected from this pin to ground for proper phasing.<br/> If an external 24 MHz signal is AC coupled to Pin 57 (XTALIN) then XTALO should be left unconnected.</p> |

| 16    | ROSC    | NA  | <p><b>ROSC: Low Frequency Oscillator Resistor</b>, ROSC determines the frequency of the low speed oscillator that is output on the micro-controller clock during power down. <b>Note:</b> Rosc and Cosc must be installed for MCUCLK output to function.</p>                                                  |

| 17    | COSC    | NA  | <p><b>COSC: Low Frequency Oscillator Capacitor</b> COSC determines the frequency of the low speed oscillator that is output on the micro-controller clock during power down.</p>                                                                                                                              |

| 15    | RBIAS   | NA  | <p><b>Bias Resistor Connection:</b> External 10.0k ohm, 1% resistor is connected to ground.</p>                                                                                                                                                                                                               |

| 27    | VREFADP | NA  | <p><b>VREF Bypass Connection:</b> External .1uF is connected to ground</p>                                                                                                                                                                                                                                    |

| 28    | VREFADN | NA  | <p><b>VREF Bypass Connection:</b> External .1uF is connected to ground</p>                                                                                                                                                                                                                                    |

| 50    | TESTEN  | I   | <p>Factory Scan Test Enable PIN: Normally grounded</p>                                                                                                                                                                                                                                                        |

| 24    | NC      | NA  | <p>Normally Disconnected</p>                                                                                                                                                                                                                                                                                  |

| 42    | NC      | NA  | <p>Factory Analog Test Pin: Normally Disconnected</p>                                                                                                                                                                                                                                                         |

| 55    | NC      | N/A | <p>Factory Analog Test Pin: Normally Disconnected</p>                                                                                                                                                                                                                                                         |

| 60    | NC      | N/A | <p>Factory Analog Test Pin: Normally Disconnected</p>                                                                                                                                                                                                                                                         |

# ALPINE LXT821

## Spread Spectrum Digital Cordless Telephone Transceiver

### 6.6 Power Supply Pins

**Table 5: Power Supply Pin Descriptions**

| Pin # | Name         | I/O | Description                                                                                                                     |

|-------|--------------|-----|---------------------------------------------------------------------------------------------------------------------------------|

| 1     | SUBVCO       | NA  | <b>VCO Substrate Connection:</b> Connect to Ground                                                                              |

| 2     | VDDRFVCO     | NA  | <b>RF VCO Frequency Synthesizer Supply:</b> Connect to VDD. Bypass with .1uF and 3.9 pF capacitor                               |

| 3     | GNDRFVCO     | NA  | <b>RF VCO Frequency Synthesizer Ground:</b> Connect to Ground                                                                   |

| 4     | GNDRFPA      | NA  | <b>Power AMP Driver Ground:</b> Connect to Ground                                                                               |

| 5     | VDDRFPA      | NA  | <b>Power AMP Driver Supply:</b> Connect to VDD. Bypass with .1uF and 3.9 pF capacitor                                           |

| 6     | GNDRFSUB     | NA  | <b>RF Substrate Connection:</b> Connect to Ground                                                                               |

| 7     | GNDRFIO      | NA  | <b>RF I/O Ground:</b> Connect to Ground                                                                                         |

| 10    | GNDRFIO      | NA  | <b>RF I/O Ground:</b> Connect to Ground                                                                                         |

| 11    | GNDRFSUB     | NA  | <b>RF Substrate Connection:</b> Connect to Ground                                                                               |

| 12    | ESDRING      | NA  | <b>ESD Ring Connection:</b> Connect to Ground                                                                                   |

| 13    | VDDRFLNA     | NA  | <b>RF Low Noise Amplifier Supply:</b> Connect to VDD. Bypass with .1uF and 3.9 pF capacitor                                     |

| 14    | GNPABIAS     | NA  | <b>PA BIAS Ground:</b> Connect to Ground                                                                                        |

| 18    | GNDBIAS      | NA  | <b>Bias Generator Ground:</b> Connect to Ground                                                                                 |

| 19    | VDDBIAS      | NA  | <b>Bias Generator Supply:</b> Connect to VDD. Bypass pin 19, 22, 25, 29, and 32 with single .1uF capacitor.                     |

| 20    | GNDMX        | NA  | <b>Mixer Ground:</b> Connect to Ground                                                                                          |

| 21    | VDDMX        | NA  | <b>Mixer Supply:</b> Connect to VDD. Bypass with .1uF and 3.9 pF capacitor                                                      |

| 22    | VDDAF        | NA  | <b>Anti-Alias Filter Supply:</b> Connect to VDD. Bypass pin 19, 22, 25, 29, and 32 with single .1uF capacitor.                  |

| 23    | GNDAF        | NA  | <b>Anti-Alias Filter Ground:</b> Connect to Ground                                                                              |

| 25    | VDDSCFAD     | NA  | <b>Switched Capacitor Circuit Supply:</b> Connect to VDD. Bypass pins 19, 22, 25, and 29 with single .1uF capacitor.            |

| 26    | GNDSCFAD     | NA  | <b>Switched Capacitor Circuit Ground:</b> Connect to Ground                                                                     |

| 29    | SOFT_DIG_VDD | NA  | <b>Timing generator, A/D and SCF digital Supply:</b> Connect to VDD. Bypass pins 19, 22, 25, and 29 with single .1uF capacitor. |

| 32    | SOFT_DIG_GND | NA  | <b>Timing generator, A/D and SCF digital GND.</b>                                                                               |

| 39    | VDDPAD       | NA  | <b>Digital PAD Driver Supply:</b> Connect to VDD. Bypass with single .1uF capacitor.                                            |

| 40    | GNDPAD       | NA  | <b>Digital PAD Driver Ground:</b> Connect to Ground                                                                             |

| 41    | SUBPAD       | NA  | <b>Digital PAD Substrate Connection:</b> Connect to Ground                                                                      |

| 51    | SUBDMD       | NA  | <b>Digital Core Substrate Connection:</b> Connect to Ground                                                                     |

| 52    | GNDDMD       | NA  | <b>Digital Core Ground:</b> Connect to Ground                                                                                   |

| 53    | VDDDDMD      | NA  | <b>Digital Core Supply:</b> Connect to VDD. Bypass pins 53 and 56 with single .1uF capacitor.                                   |

| 56    | VDDXO        | NA  | <b>Crystal Oscillator Supply:</b> Connect to VDD. Bypass pins 53 and 56 with single .1uF capacitor.                             |

| 59    | GNDXO        | NA  | <b>Crystal Oscillator Ground:</b> Connect to Ground                                                                             |

| 61    | GNDSYN       | NA  | <b>Synthesizer Divider Ground:</b> Connect to Ground                                                                            |

| 62    | VDDSYN       | NA  | <b>Synthesizer Divider Supply:</b> Connect to VDD. Bypass with .1uF and 3.9 pF capacitor                                        |

### 7. Interfaces and Functions

# ALPINE LXT821

## Spread Spectrum Digital Cordless Telephone Transceiver

### 7.1 RF Interface Description

The RF interface consists of one Bi-directional Balanced RF port and requires two pins.

During the **Transmit Mode** the RFIO and RFION terminals serve as the balanced Transmit Power Amplifier output terminals.

During the **Receive Mode** the RFIO and RFION terminals serve as the balanced Low Noise Amplifier input terminals.

During either the **Ready Mode** or the **Power Down Mode** both RFIO and RFION revert to a high impedance state.

#### 7.1.1 Balanced RF Input and Output

Negative side RFION, Pin 8

Positive side RFIO, Pin 9

ALPINE connects to an antenna through a network of balanced matching components, a balun, a 50 Ohm ISM band pass filter and a single ended 50 Ohm to antenna impedance matching network

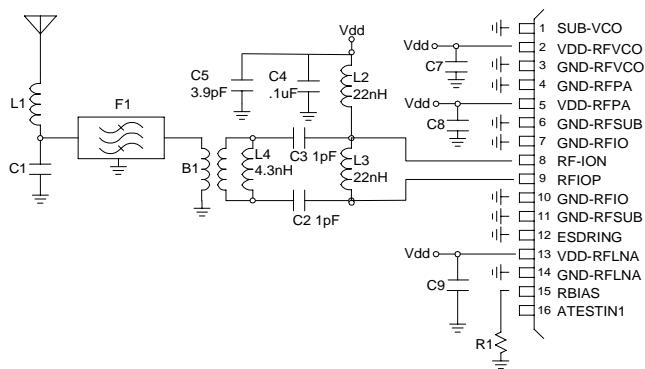

Figure 3: RF Input and Output

Inductors L2 and L3 are RF chokes that provide DC bias current to the RFION and RFIO balanced RF I/O port. Capacitors C4 and C5 provide a RF ground at the Vdd terminal to L2 and L3. Vdd, L2, C4, and C5 can be connected on either side of L3. This unsymmetrical bias arrangement minimizes the power supply trace length to pins 8 and 9. This is done to eliminate potential instability at the RF I/O pins 8 and 9. The .1uF capacitor provides low frequency bypass and the 3.9 pF capacitor provides bypass at 2.4 GHz.

Components C2, C3 and L4 convert the complex impedance looking into RFION and RFIO into 50 Ohms when monitored differentially across L4.

A balanced to unbalanced transformer (Balun) is used to convert the 50 Ohm differential signal to a 50 Ohm single ended signal. A 50 Ohm ISM band two pole ceramic resonator filter is used to help reject out of band signals. Matching components L1 and C1 convert the antenna impedance to 50 Ohm. Components L1 and C1 depend strongly on the type of antenna used and the size and shape of the printed circuit board ground plane.

# **ALPINE LXT821**

*Spread Spectrum Digital Cordless Telephone Transceiver*

## Notes:

It is possible to use etched printed circuit board inductors and Balun for lower cost.

Other implementations, such as, fully differential antenna, filter and impedance circuits are possible.

When combined with external active components such as low noise amplifiers, power amplifiers and PIN diode RF switches, it is possible to decrease the system noise figure and increase the available system output power; however, this is not recommended for low cost systems. If an external power amplifier is used, care must be taken during IC power up; the default condition places the IC into an active transmit mode at maximum output power. Refer to figure 18 for more details.

### 7.1.2 Synthesizer Phase Lock Loop

**Table 6** Synthesizer Specifications

| Parameter                                | Symbol      | Min | Typ | Max | Units | Test Conditions                    |

|------------------------------------------|-------------|-----|-----|-----|-------|------------------------------------|

| Power Down To Synthesizer Lock Time      | $T_{PDRDY}$ | --- | --- | 2   | μS    | Utilizing Synthesizer Test Circuit |

| Channel Change Time                      | $T_{CH}$    | --- | --- | 1   | μS    | Utilizing Synthesizer Test Circuit |

| Phase Locked Loop Closed Loop Band Width | $BW_{PLL}$  | 2.5 | 5   | 10  | kHz   | Utilizing Synthesizer Test Circuit |

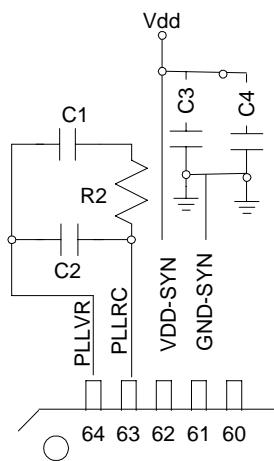

**Figure 4: Synthesizer Test Circuit**

## Synthesizer Test Circuit Component Values:

C1 = 0.2 uF, R2 = 2 k ohm, C2 = 0.01uF, C3 = 0.1uF, C4 = 3.9 pF

The synthesizer phase lock loop bandwidth (PLL BW) can be changed by using either a high charge pump current or a low charge pump current. The high and low charge currents can be independently adjusted to 0 uA, 100 uA, 200 uA, 300 uA, 400 uA, 500 uA, 600 uA, or 800 uA by accessing registers 5B and 5C respectively.

## ALPINE LXT821

### Spread Spectrum Digital Cordless Telephone Transceiver

Default operation will configure the PLL to use a low charge pump current of 100 uA. There is an option that will automatically enable the high charge pump current during transitions on the transmit enable and receive enable signals. This will increase PLL BW during supply current spikes thereby attenuating transmit spurs. This feature is normally disabled. The duration of high charge pump current operation is controlled by register 53.

Register 57 controls which charge pump current value is used and can enable the automatic charge pump switch.

When the channel frequency is changed the charge pump current should be set to 800 uA for 250 uS. If this is not done, the PLL can become unstable and lose lock during a channel change. The recommend channel change procedure is:

- Program register 57 = 0D hex: enable 800 uA high charge pump current

- Change channels by writing to registers 40, 41, and 42.

- Wait 250 uS

- Program register 57 = 04: enable 100 uA low charge pump current

This channel changing procedure will result in a maximum PLL settling time of 3 mS. PLL lock time will be 1mS or less.

The low charge pump current default value is 100 uA and the high charge pump current default value is 800 uA; therefore, registers 5B and 5C should never be reprogrammed.

**Note:**

The transmit power amplifier will automatically shut down if the PLL goes out of lock. This is done to eliminate unwanted radiation outside of the ISM band. This situation can arise due to a low supply voltage, a transition from the power down state to the ready state, or a channel change.

# ALPINE LXT821

## Spread Spectrum Digital Cordless Telephone Transceiver

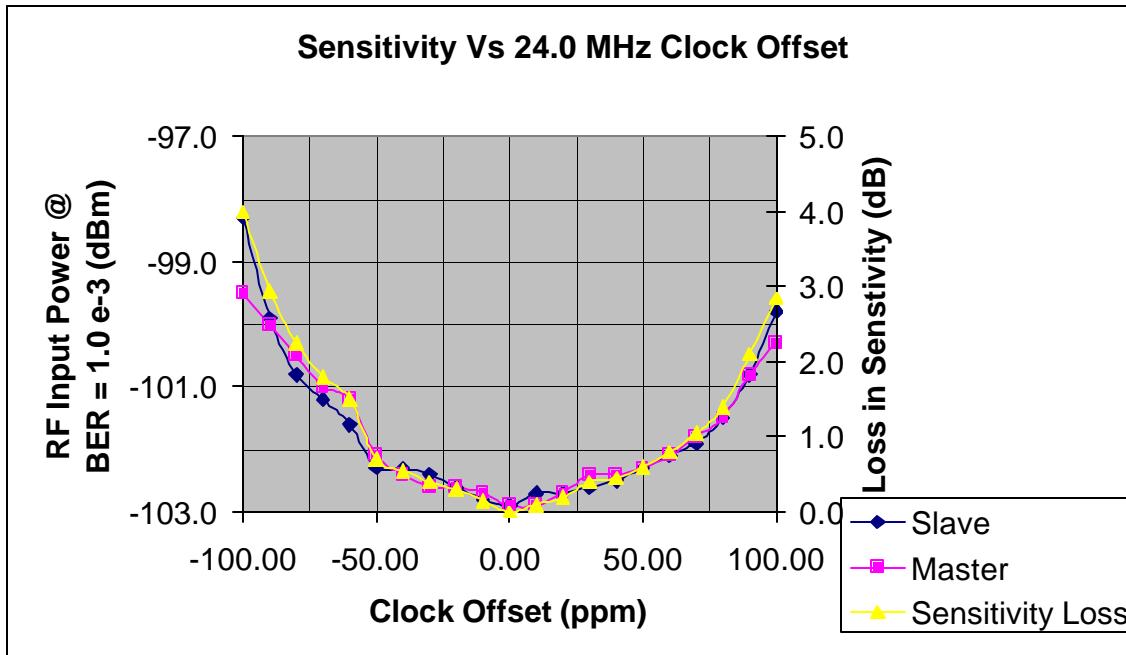

### 7.1.3 Crystal Clock

Table 7: Crystal Oscillator Specifications

| Parameter                                                                                                                 | Symbol               | Min   | Typ        | Max        | Units           | Test Conditions                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------|----------------------|-------|------------|------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Externally applied XTALIN Voltage, AC coupled                                                                             | V <sub>XI</sub>      | 0.3   | 1          | 2.0        | V <sub>PP</sub> | AC coupled                                                                                                                                                 |

| Externally applied XTALIN Duty Cycle                                                                                      | D <sub>Cycle</sub>   | 45/55 | 50/50      | 55/45      | %               | AC Coupled                                                                                                                                                 |

| XTALIN Pin capacitance                                                                                                    | C <sub>XI</sub>      | ---   | 1.7        | 2          | pF              |                                                                                                                                                            |

| XTALO Pin capacitance                                                                                                     | C <sub>XO</sub>      | ---   | 1.7        | 2          | pF              |                                                                                                                                                            |

| XTAL Oscillator Frequency Accuracy                                                                                        | F <sub>XO</sub>      | -30   | 0          | +30        | ppm             | Total frequency variation due to both temperature and frequency accuracy.<br><br>See test circuit below.<br>Frequency measured at CODECCLK or MCUCLK pins. |

| XTAL Oscillator Duty Cycle                                                                                                | D <sub>CycleXO</sub> | 45/55 | 50/50      | 55/45      | %               | See test circuit below.<br>Duty Cycle measured at CODECCLK pin.                                                                                            |

| Oscillator Turn On Time After Supply Power Up:<br>After Power Down Disable:                                               |                      |       | 2.0<br>0.5 | 5.0<br>1.0 | mS              | See test circuit below.<br><b>Note:</b> Turn On Time dependent on crystal specifications.                                                                  |

| Crystal Signals Include; XTALIN and XTALO<br>Crystal Oscillator Measurements are at 25 °C and V <sub>DD</sub> = 3.3 Volts |                      |       |            |            |                 |                                                                                                                                                            |

# ALPINE LXT821

## Spread Spectrum Digital Cordless Telephone Transceiver

Figure 5: Crystal Oscillator test Circuit

# ALPINE LXT821

## Spread Spectrum Digital Cordless Telephone Transceiver

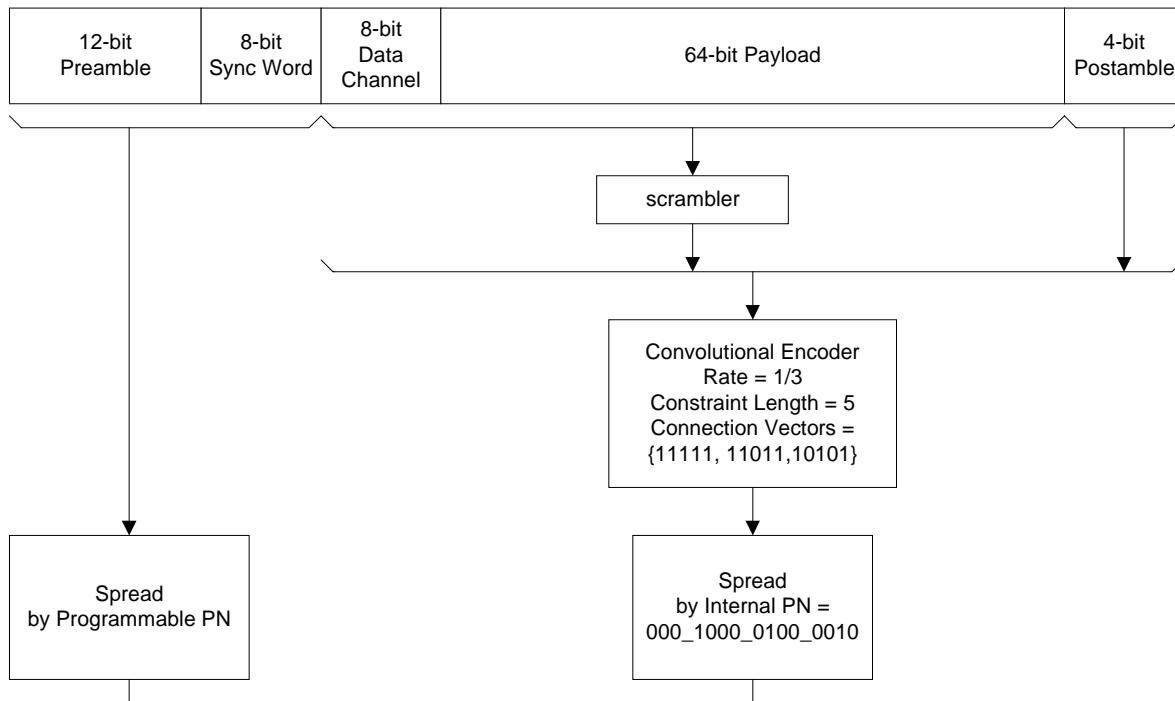

### 7.2 Channel Coding and Direct Sequence Spreading

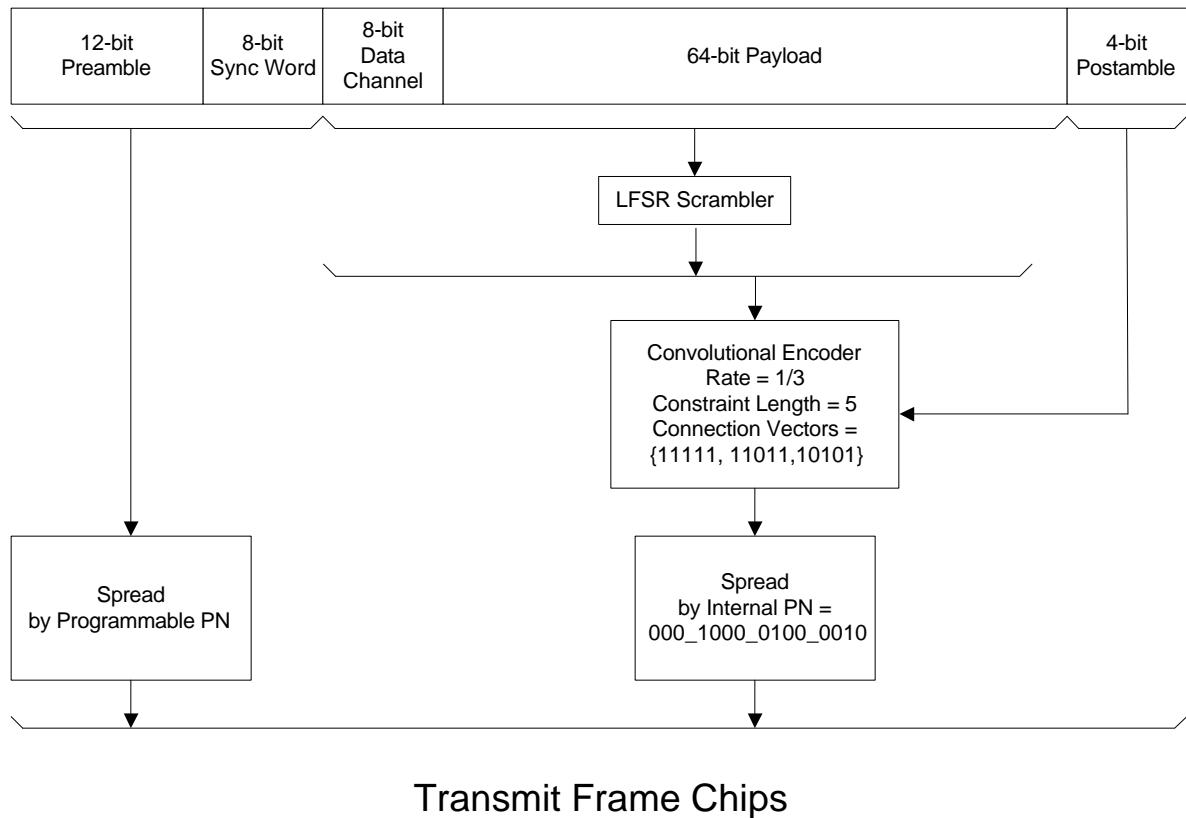

The various segments of the transmitted frame undergo different coding treatment and are spread by different PN sequences.

- The Preamble and Sync Word are spread with the user programmable PN code in PNREG1 and PNREG2 (addresses 0x00 and 0x01).

- The Data Channel and Voice / Fast Data Channel (FDC) Payload are scrambled, run through a rate 1/3 convolutional encoder, and spread with a preset, non-programmable, PN code.

- The Post-amble is treated the same as the Data Channel and Payload except that it is not scrambled; the four post-amble bits are always equal to zero.

**Figure 6, Channel Coding and Spreading**

### Transmit Frame Bits

### Transmit Frame Chips

#### 7.2.1 Spreading

Each bit is spread by a 15-bit PN code. The spreading is exactly in phase with the start of the bit; start of Most-Significant-Chip coincides with start of bit. The user programmable PN is contained in registers 0x00 and 0x01.

# ALPINE LXT821

## Spread Spectrum Digital Cordless Telephone Transceiver

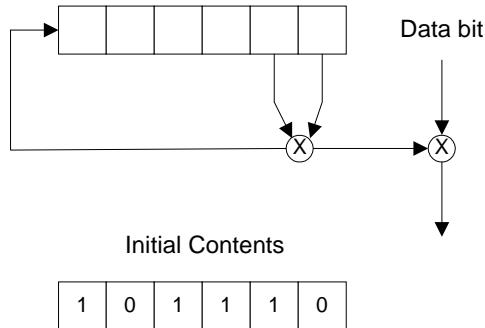

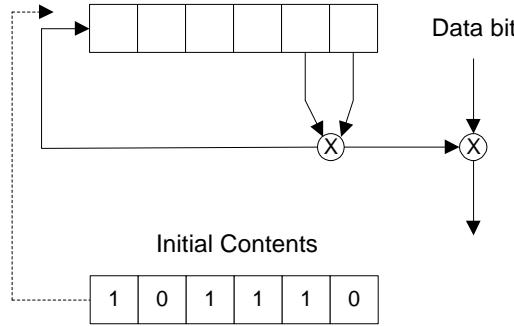

### 7.2.2 Scrambler

Data scrambling is done with an LFSR:

Figure 7, Data Scrambler LFSR

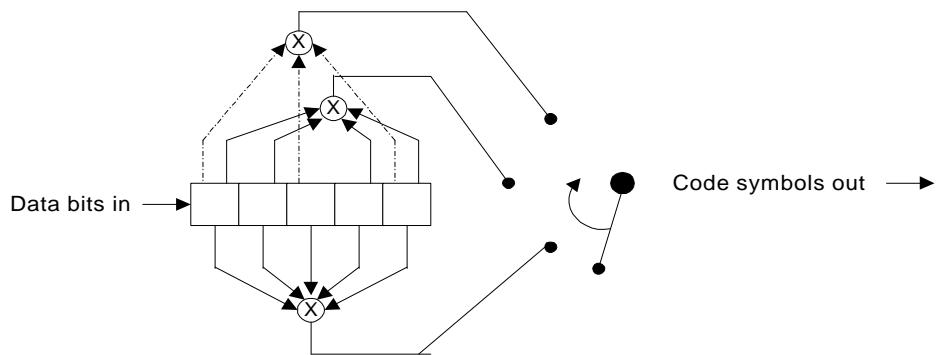

### 7.2.3 Convolutional Encoder

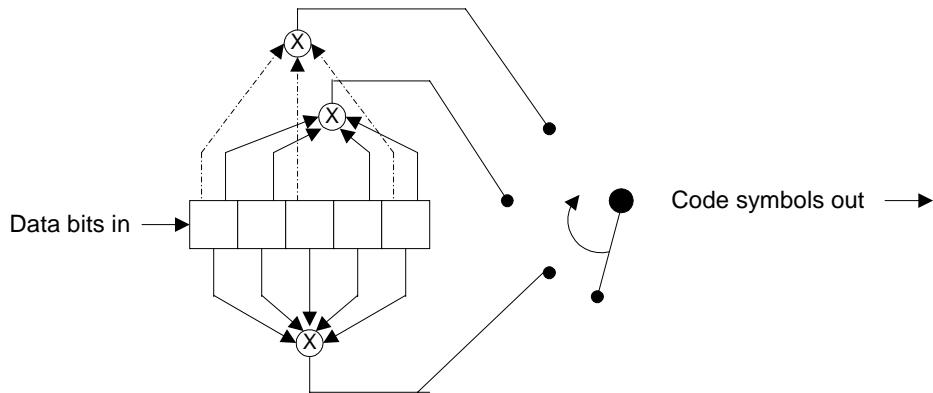

Figure 8 illustrates the Alpine convolutional encoder in so-called connection representation. In this representation, the encoder action is imagined to take place in two stages: First a bit is shifted into the shift register from the left, the rightmost bit being shifted out. Second, the rotary switch rotates, touching each of the three contacts in turn. The constraint length is 5, meaning that the shift register is 5 message bits wide. The code rate is 1/3 meaning that one message bit results in three code symbols. The three code symbols occupy one bit period.

Figure 8, Alpine Convolutional Encoder

The connection vectors are the shift register taps. The vectors used in the Alpine encoder are well known optimal performing vectors for constraint length five and rate 1/3. Optimal means that the encoder is non-catastrophic and has maximal Hamming distance between code word sequences. (A catastrophic encoder has the property that certain finite sequences of erroneous code symbols will cause the decoder to decode an infinite sequence of bit errors.)

# ALPINE LXT821

## Spread Spectrum Digital Cordless Telephone Transceiver

### 7.3 ADPCM CODEC Interface

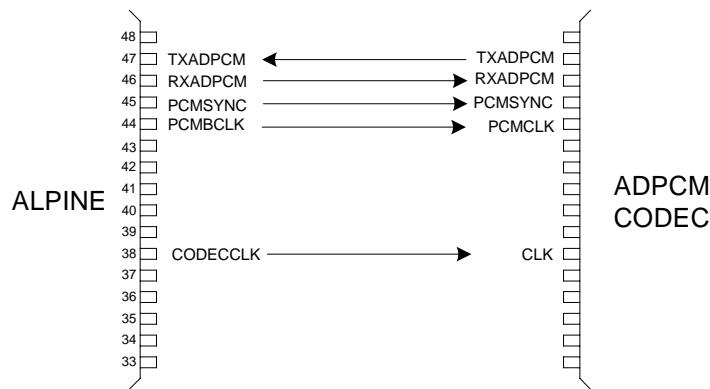

**Figure 9 ALPINE / CODEC Interface Connections**

The interface to the ADPCM Codec consists of five signal lines:

- TXADPCM – 32 k b/s voice data coming from the Codec to be transmitted over the RF link

- RXADPCM – 32 k b/s voice data received over the RF link to be output to the Codec

- PCMBCLK - A 32 kHz or 64 kHz bit clock

- PCMSYNC - An 8 kHz PCM Sync signal

- CODECCLK - A 19.2 MHz or 24.0 MHz clock used to drive the master clock input to the Codec. Can be deactivated if necessary.

# ALPINE LXT821

## Spread Spectrum Digital Cordless Telephone Transceiver

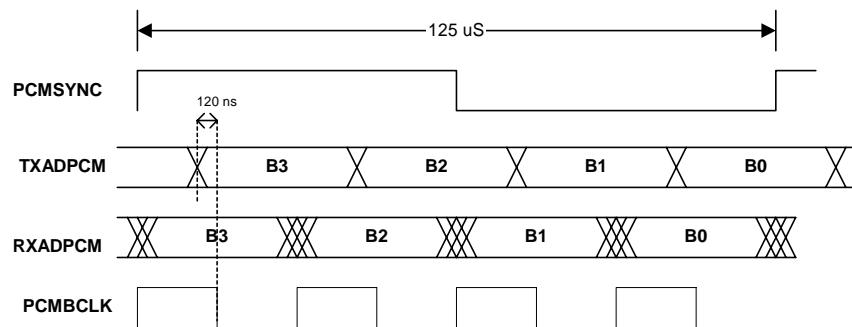

### 7.3.1 ADPCM timing

The ADPCM Codec interface can be set to operate in one of two timing modes. These two modes are implemented to ensure compliance with different ADPCM Codec interface requirements

#### 7.3.1.1 Mode 0

Mode 0 provides a continuous, non-gapped 32k b/s interface, which allows for simplified link BER testing

Operation in ADPCM Mode 0 (Register 0F **CLKCTRL[4]** = 0) is shown below

Figure 10: ADPCM Interface Timing Diagram Mode 0

**Errata:** In the LXT821A1 and LXT821B1, if the IC is operated in slave mode, the TXADPCM is sampled on the rising edge. The other TXADPCM and RXADPCM signals are sampled on the falling edge, whether Alpine is operated as either a slave or master mode.

#### 7.3.1.2 Mode 1

Mode 1 is compliant with the OKI 7570L series ADPCM codec as well as codecs manufactured by AKM and others. Operation in ADPCM Mode 1 (Register 0F **CLKCTRL[4]** = 1) is shown below

Figure 11: ADPCM Interface Timing Diagram Mode 1

# ALPINE LXT821

## Spread Spectrum Digital Cordless Telephone Transceiver

### 7.4 Micro-Controller Interface Description

The Micro-Controller (MCU) interface provides external control and monitoring of all internal functions. The MCU interface is compatible with the industry standard Motorola Serial Peripheral Interface (SPI) bus. The SPI bus is organized in a master/slave manner\*, with the host MCU usually being the master. ALPINE must be used as a SPI slave device.

\*- **Note:** no relationship to TDD Master/Slave protocol operation

#### 7.4.1 SPI Bus Description

The SPI bus used in ALPINE consists of the following four signals:

##### 7.4.1.1 Micro-Controller Master CLK Output (MCUCLK)

Clock for input to the MCU. This clock can be programmed to a frequency of either 100kHz, 2, 4, 6, or 12 MHz using CLKCTRL[2:0].

This clock is switched to a low-frequency (100 kHz) standby oscillator when PWRDN[5] is asserted. The operating frequency of the low-speed clock is set by the capacitor and resistor connected to the COSC and ROSC pins. It is possible to increase this clock frequency to 200 kHz.

**Note:** The higher speed MCU clocks are divided down from the 24 MHz crystal clock. In addition, the circuit that switches between the high-speed and low-speed clocks is designed to be glitch-free, eliminating the possibility of generating fractional clock cycles during a switch-over. This circuit requires that both clocks be active during the switchover. The external components at the ROSC and COSC are required for the MCU clock output to operate, regardless of selected operating frequency.

##### 7.4.1.2 SPI Data In (SPIDIN)

Data input for byte-wise data transmitted serially from the MCU, MSB first.

##### 7.4.1.3 SPI Data Out (SPIDOUT)

Data Output for byte-wise data transmitted serially to the MCU, MSB first. Data transitions are on the falling edge of SPI CLK and the data is sampled by the MCU on the rising edge of SPICLK. **Note:** SPIDOUT is only made active when SPIEN is low and the SPI register being read from is within Alpine's 00h to 7Fh address space. Otherwise, SPIDOUT is placed in the high-impedance state.

##### 7.4.1.4 SPI Clock In (SPICLK)

Serial clock to synchronize the data movement both in and out of Alpine. See timing diagrams in both **Figure 12** and **Figure 13** below.

##### 7.4.1.5 SPI Enable (SPIEN)

The SPI EN line is used to select ALPINE as a slave device for data transactions. It must be low prior to the beginning of a transaction and must stay low for the duration of the transaction.

# ALPINE LXT821

## Spread Spectrum Digital Cordless Telephone Transceiver

### 7.4.2 SPI Protocol Description

The SPI bus is a byte-wise serial transmission link between the system MCU and peripheral devices. To translate the byte-wise serial nature of the SPI bus to Alpine's register-mapped I/O, it uses the following protocol to communicate via the SPI bus. A typical ALPINE SPI bus transaction consists of two SPI bus operations, first the MCU transmits the address byte of the register to be written to/read from, after which the MCU or ALPINE outputs the data byte, depending on whether a read or write operation was indicated (see below).

A SPI read or write is initiated by asserting SPIEN (active low), whose falling edge resets the internal SPI controller state machine, readying it for the first (address) byte. The MSB of the address byte (A[7]) indicates whether a read or write transaction is to be performed. A[7] is high for read operations and low for write operations. The remaining address bits (A[6:0]) address the individual registers in the ALPINE register map.

**Note:** Alpine's register map is divided into 3 sections. The analog section of the IC uses a Intel proprietary "Quiet Bus Technology" based on a Three Wire Interface (TWI) for minimum interference and area purposes. These 4-bit registers are accessed externally via the SPI interface, and are mapped to the low order nibble of addresses from 40h to 7Fh. The Burst Mode Controller section uses standard 8-bit SPI registers, which are mapped to addresses from 00h to 2Fh. The remainder of Alpine's 8-bit registers are mapped to addresses from 30h to 3Fh. Registers 40h and higher are not accessible during power down operation as they require a functioning 24.0 MHz clock.

### 7.4.3 SPI Write Operation

For a Write operation, the MCU first asserts SPIEN, and then outputs the address byte of the register to be accessed, with the MSB of the address byte (A7) set low. After all 8 address bits are transmitted the MCU outputs the data byte to be written into the addressed register, MSB first. Finally the MCU de-asserts the SPIEN line to high.

Figure 12: SPI Bus Write Operation Timing Diagram

# ALPINE LXT821

## Spread Spectrum Digital Cordless Telephone Transceiver

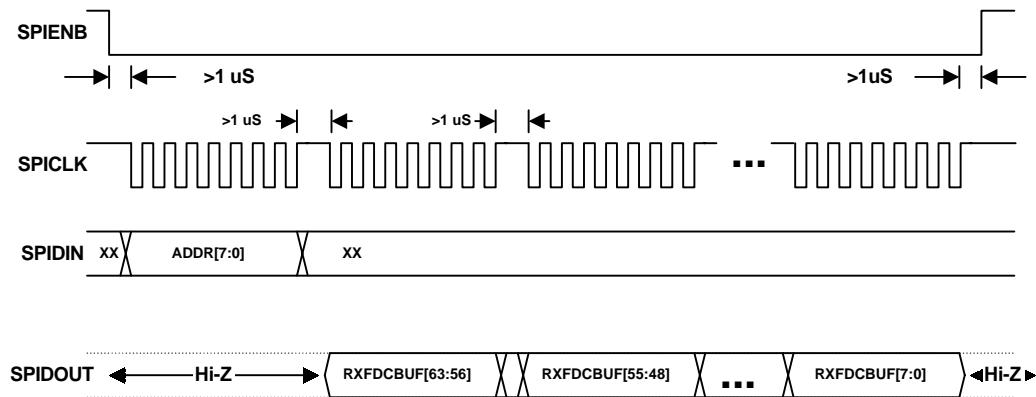

### 7.4.4 SPI Read Operation

For a Read operation, the MCU first asserts SPIEN, and then outputs the address byte of the register to be accessed, with the MSB of the address byte (A7) set high.

After all 8 address bits are transmitted the MCU issues a SPI Read command, which produces 8 cycles of SPICLK. The BMC responds by outputting the data byte read from the addressed register on SPIDOUT, MSB first, with transitions on the falling edges of SPI CLK. Finally the MCU de-asserts the SPIEN line to high.

Figure 13: SPI Bus Read Operation Timing Diagram

For more information on SPI bus operation, refer to the Motorola 68HC705 technical manual

### 7.4.5 Fast Data Channel

The Fast Data Channel (FDC) allows the system MCU to write/read from the 64-bit payload field of the TDD frame. This gives the MCU a much faster communications channel between handset and base when there is no need to send ADPCM voice data (i.e. when on-hook).

The Fast Data Channel mode uses the FDCCTRL, TXFDCBUF, and RXFDCBUF registers to provide a 32k b/s end-to-end high-speed data link.

To enable the Fast Data Channel, the system MCU must set the TX FDC Enable and RX FDC Enable bits (FDCCTRL[4] and FDCCTRL[0]).

# ALPINE LXT821

## Spread Spectrum Digital Cordless Telephone Transceiver

### 7.4.5.1 TX Fast Data Channel Operation

The TX FDC buffer is a double-buffered 64-bit register that is copied into the TX payload field when **FDCCTRL[4]**=1. To write to the TX FDC Buffer, the MCU writes to the 64-bit TXFDC buffer (TXFDCBUF) with a 9-byte SPI bus operation as follows.

The MCU first outputs the TXFDCBUF address (09h), clearing the read / write bit. The MCU then writes eight bytes in succession which contain the 64 bits to be transmitted over the RF link. When ALPINE has received the eighth byte, it sets the TXFDC status flag (FDCCTRL[7]), and waits for the next TX frame to insert the contents of the TX FDC buffer into the outgoing TX payload field.

Once the payload has been output, the TX FDC status flag is cleared.

**Note:** If the write operation is aborted before all nine bytes have been received over the SPI bus (by disabling SPIEN), the contents of the TX FDC buffer will not be updated, and will contain the contents of the last successfully completed write operation.

In addition, as long as **FDCCTRL[4]** is set, the outgoing TX payload field will continue to transmit the contents of the TX FDC buffer regardless of whether the buffer has been updated since the last outgoing TX frame.

Figure 14: TX Fast Data Channel Write Operation Timing Diagram

# ALPINE LXT821

## Spread Spectrum Digital Cordless Telephone Transceiver

### 7.4.5.2 RX Fast Data Channel Read

The RX FDC buffer is a double-buffered 64-bit register that is loaded with the RX payload field when **FDCCTRL[0]**=1. When RX FDC operation has been enabled (**FDCCTRL[0]** = 1), ALPINE waits for the next incoming RX frame, and then loads the contents of the incoming 64-bit payload field into the RX FDC buffer and sets the RX FDC status flag (**FDCCTRL[3]**).

To read the contents of the RX FDC Buffer, the MCU reads from the 64-bit RX FDC buffer (RXFDCBUF) with a 9-byte SPI bus operation as follows.

The MCU first outputs the RXFDCBUF address (0Ah), setting the read / write bit. The MCU then reads eight bytes in succession which contain the 64 bits received in the last incoming RX frame. When ALPINE has received the eighth byte, it clears the RXFDC status flag (**FDCCTRL[3]**), and waits for the next incoming RX frame.

The contents of the RX FDC buffer will be written over by each successive received frame, regardless of whether the MCU reads the contents of the RX FDC buffer.

**Note:** If the read operation is aborted before all nine bytes have been received over the SPI bus (by disabling SPIEN), the RXFDC status flag will not be cleared.

Figure 15: RX/TX Fast Data Channel Read Operation Timing Diagram

# ALPINE LXT821

## Spread Spectrum Digital Cordless Telephone Transceiver

### 7.4.6 MCU Interrupt output (IRQ)

ALPINE provides an interrupt output, IRQ, to synchronize the MCU to the TDD burst timing. The IRQ output can be programmed to present up to two interrupts per TDD frame. Each interrupt consists of a 10 uS negative-going pulse. The number and timing of each interrupt is programmed in the **IRQFRMT** register.

The TX and RX slots each have their own interrupt, which can be independently enabled or disabled. When enabled, each TX/RX slot interrupt can be programmed to occur at either the beginning or end of their respective payload fields. The timing of these locations is shown below.

The IRQFRMT register controls the operation of the IRQ output. **IRQFRMT[1:0]** enables and sets the location of the RX interrupt, while **IRQFRMT[3:2]** enables and sets the location of the TX interrupt.

The IRQ TX/RX flag, **IRQFRMT[7]**, indicates whether the last interrupt generated was a TX interrupt or an RX interrupt. The flag is set upon generation of a TX interrupt, and cleared upon generation of an RX interrupt. If RX interrupts are disabled, the flag stays set, and if TX interrupts are disabled, the flag stays cleared.

Master/Slave behavior of the interrupts are as follows:

In Master mode, both the TX and RX interrupts are generated off of the free-running master clock. The TX slot interrupt occurs 330 uS after the rising edge of TXEN if **IRQFRMT[3:2]** = 01, or occurs 970 uS after the rising edge of TXEN if **IRQFRMT[3:2]** = 10. Note that TX interrupts are generated regardless of the state of the TX disable/abort bits **TXFRMT[4:3]**.

The RX interrupt is generated 1340 uS after the rising edge of TXEN if **IRQFRMT[1:0]** = 01, or occurs 1980 uS after the rising edge of TXEN if **IRQFRMT[1:0]** = 10. Note that the RX interrupt timing is not synchronized to the incoming RX slot, and the reference to its timing relationship to the incoming RX slot is approximate only. Also, RX interrupts are generated regardless of the sync state of the master, so that RX interrupts will be generated even if there is no incoming RX signal. Lastly, RX interrupts are generated regardless of the state of the RX disable bit **RXFRMT[4]**.

When in Slave mode and Frame Sync has not been obtained there is not a true TDD frame defined. Internally, though, the unit does generate the Frame timing signals as illustrated below in **IRQ Interrupt Timing**. The interrupt enable modes are then based on this internal timing structure. Thus if interrupts are enabled with respect to the TX Payload, either start or end, there will be an interrupt generated at the proper time according to the internal Frame timing signals. When Frame Sync is obtained, the frame and interrupt timing will be changed to correspond to the TDD frame timing then put into effect.

**Note:** The default value of **IRQFRMT[7:0]** = 00 hex disables all interrupt signals. This may be a critical consideration during power up.

# ALPINE LXT821

## Spread Spectrum Digital Cordless Telephone Transceiver

Figure 16- IRQ Interrupt Timing

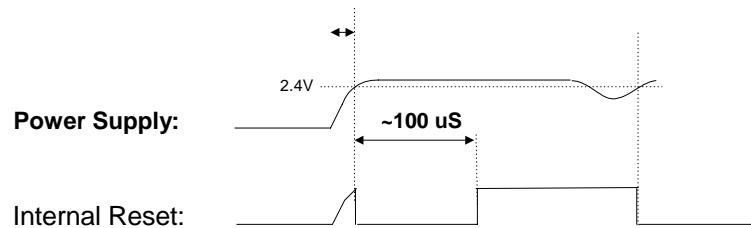

#### 7.4.7 RESET

ALPINE has an internal reset mechanism that is initiated two different ways:

- A supply voltage generated reset (power up reset). If the supply voltage crosses 2.4 volts and is increasing with time, a reset will be initiated. A reset will not be initiated if the supply voltage crosses 2.4 volts and is decreasing with time.

- An external reset pin (36). A low to high transition will initiate a reset.

Both mechanisms are logically OR'ed internally; each mechanism will generate a high-to-low transition on an internal reset signal. The internal reset will remain low for 100 uS and then return to a high state. This low to high transition will start the reset process. This will reset all internal state machines in Alpine (SPI, TDD Timing Generator) as well as restore all programmable registers to their default values. The reset sequence will be complete 1.3 to 1.4 mS after initiation.

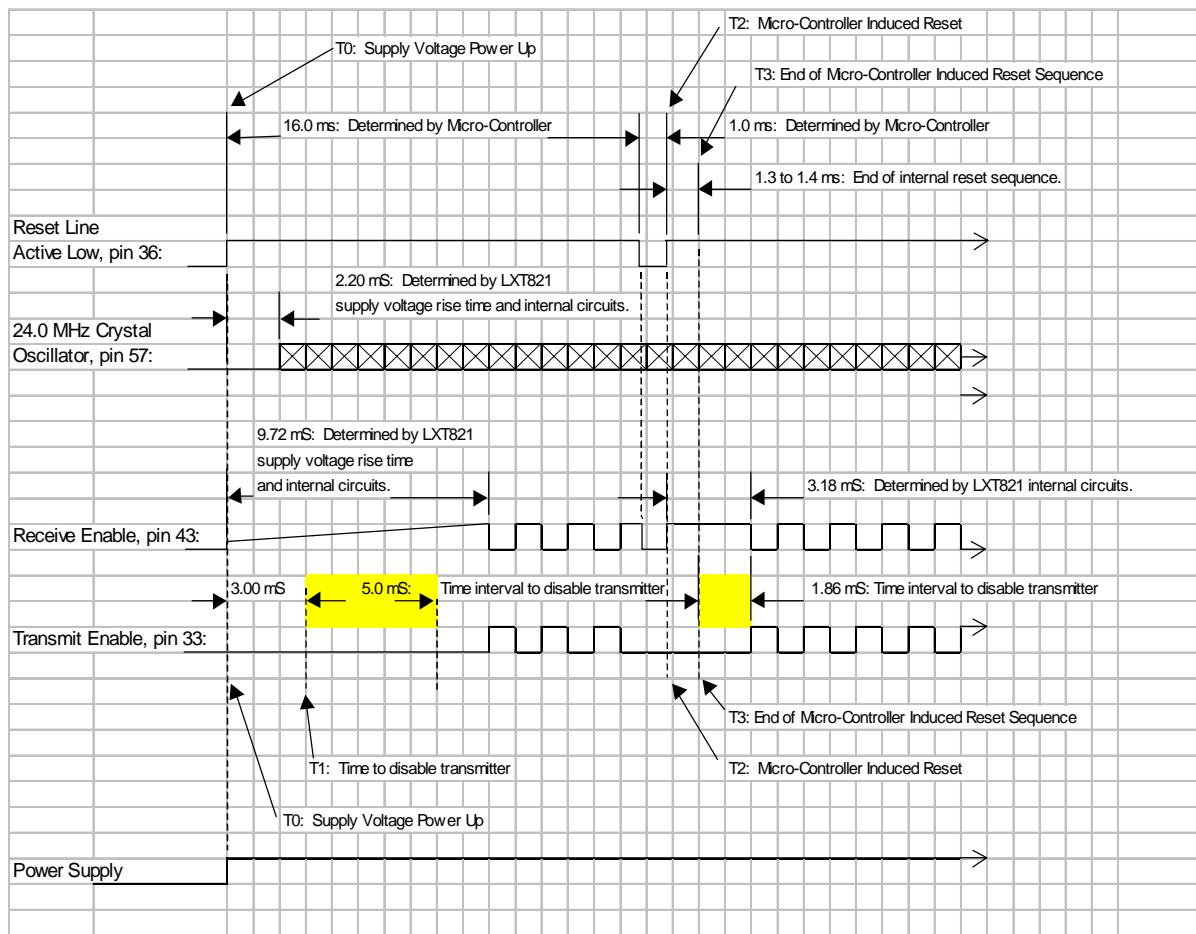

**Figure 17: Power Up Reset Timing Vs Power Supply Voltage**

A reset will configure Alpine into the following operating mode:

- Master Mode

- Channel Frequency = 2.4405 GHz

- Output Power = 20 dBm

- All IRQ signals disabled

- ADPCM Mode = 0

- MCU clock frequency = 2.0 MHz

- MCU low speed oscillator enabled but not active

- Codec clock disabled

This means that during under normal power up, Alpine will start transmitting power if no register commands are sent.

To prevent transmission after power up, the transmitter should be disabled during the time intervals indicated in figure 18:

## ALPINE LXT821

### Spread Spectrum Digital Cordless Telephone Transceiver

**Figure 18: Reset Timing**

In order to access registers with an address of 40 hex or greater, the 24.0 MHz oscillator must be active. This oscillator will be fully operational 2.0 to 5.0 mS after initiation of a power up reset.

#### 7.4.8 Power Down (PWRDN)

There are three power-down signals in ALPINE:

- A BMC power-down, which is used to place the BMC portion of ALPINE in a dormant, low-power state

- An RF sub-circuit power-down mode, used to turn off all analog and digital RF circuitry

- An LFOSC enable signal to switch on the low-frequency MCU standby oscillator

## ALPINE LXT821

### Spread Spectrum Digital Cordless Telephone Transceiver

#### 7.4.8.1 BMC Power Down

Setting the BMC PWRDN bit, **PWRDN[6]**, places all internal ALPINE BMC circuitry into a low-power state.

**Note:** In order to be immune to a slow decay of clock amplitude (resulting from the crystal clock being powered down), a switchover must be made to the LFOSC before **PWRDN[6]** is set.

When in the BMC PWRDN state, ALPINE I/Os assume the following conditions:

- Digital Outputs generally retain last set values.

- The SPI MCU Interface remains operational

#### 7.4.8.2 RF Power Down

Setting the RF PWRDN bits, **PCNTEN[3:0]=1001**(hex address 33), places all internal ALPINE RF circuitry into a low-power state.

**Note:** when powering down via SPI register commands, the BMC section should be turned off before the radio section. In addition, the radio section should be turned on for at least 1.0 mS before the BMC section is turned on. This guarantees that a glitch free 24.0 MHz clock is available to the BMC section.

#### 7.4.8.3 External Power Down Pin

Tying pin 37 to the power supply will place entire IC into power down mode.

**Errata:** The external power down pin (37) only turns off the radio section in the LXT821A1. In both the LXT821A1 and LXT821B1, the external power down pin does not reset the receiver state machine. To assure reliable operation, the BMC should be disabled by PWRDN[6] before enabling the external power down. In addition, the external power down should be disabled for at least 1mS before the BMC is enabled by PWRDN[6].

#### 7.4.9 Low-speed MCU Clock

The following two register bits control the low-frequency MCU standby oscillator (LFOSC):

- The LFOSC enable bit **PWRDN[5] = 1** enables the low-speed MCU standby oscillator.

- The MCUCLK select bits **CLKCTRL[2:0] = 100** selects the LFOSC output to drive the MCUCLK output.

The switchover circuit in the MCU clock selector requires both clock sources to be enabled prior to a switch from one clock source to another, to ensure a glitch-free switchover. Therefore, it is recommended that a switchover be controlled by the MCU in the following manner:

**Note:** Upon power-up, the LFOSC is enabled but inactive. The MCUCLK upon power up is 2.0 MHz.

To switch over to the high-speed MCUCLK:

- Enable the ALPINE Transceiver, 24 MHz oscillator, and BMC sections by setting **PCNTEN[0] = 0** and then **PWRDN[6] = 0**.

- Switch to the HF MCUCLK by setting **CLKCTRL[2:0] = 000** (2MHz), **001** (4 MHz), **010** (6 MHz), or **011** (12 MHz).

- Disable the LFOSC by setting **PWRDN[5] = 0**.

To switch over to the low-speed MCU clock:

- Enable the LFOSC by setting **PWRDN[5] = 1**.

- Switch to the LF MCUCLK by setting **CLKCTRL[2:0] = 100**

## ALPINE LXT821

### Spread Spectrum Digital Cordless Telephone Transceiver

- Disable the ALPINE BMC and Transceiver sections by setting **PWRDN[6] = 1** and **PCNTEN [3:0] = 1001**.

The low speed oscillator requires the external components COSC and ROSC indicated in Table 8.

| Standby<br>Oscillator<br>Frequency | COSC value | ROSC value   |

|------------------------------------|------------|--------------|

| 100 kHz                            | 68 pF, 1%  | 470 kOhm, 1% |

| 200 kHz                            | 68 pF, 1%  | 220 kOhm, 1% |

**Table 8 - Standby Oscillator Component Values**

**Note:** if these components are not installed, the high speed MCU Clock will not operate.

Typical powerdown current is around 120 uA when the low speed oscillator is enabled; however, the power down current can be reduced to around 55 uA if the low speed oscillator is disabled. The low speed oscillator can be disabled by not installing the external components listed in Table 8 or by setting ALPCTRL[7] = 1, hex address 05. If these two options are implemented, a second MCU clock source is required.

#### 7.5 Spread Spectrum Processor/Burst-mode Controller Description

The Spread Spectrum Processor / Time Division Duplex (TDD) Burst-mode Controller (BMC) does the spreading and de-spreading of the TX and RX data, and controls the TDD operation of the spread spectrum digital cordless telephone (SSDCT) system. This includes the spread spectrum generator, the receive correlator / de-spreader and timing recovery, framer / de-framer, and FIFO for buffering incoming ADPCM voice data.

The BMC block consists of the following sections:

- Transmit Framer and Direct Sequence Spread Spectrum generator.

- Timing generator and TDD controller.

- Receive side correlator /de-spreader with bit clock recovery loop.

- Receive side framer and data de-multiplexer.

- Link Quality Monitor to provide for status monitoring of the RF link, including Link Quality Alarm.

- 32k b/s ADPCM interface with TX/RX FIFO buffers

- TX and RX Fast Data Buffers which allow the system MCU to write/read data to/from the 32k b/s voice payload field .

# ALPINE LXT821

## Spread Spectrum Digital Cordless Telephone Transceiver

Figure 19 - Functional Block diagram of the Spread Spectrum Burst Mode Controller

# ALPINE LXT821

## Spread Spectrum Digital Cordless Telephone Transceiver

### 7.5.1 BMC TDD Frame Format – normal mode

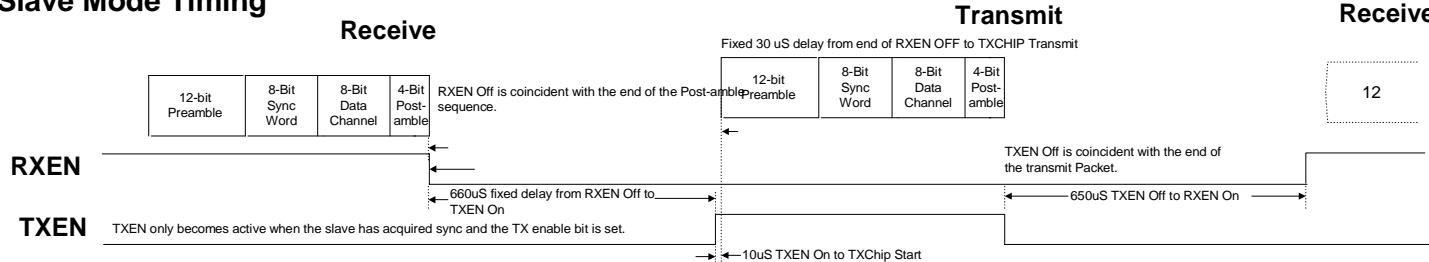

The BMC uses the TDD frame format shown in Figure 20 when set to normal mode (TXFRMT[6] and RXFRMT[6] set to 0)

#### Master Mode Timing

#### Slave Mode Timing

Figure 20 TDD Frame Format of BMC (normal mode)

## ALPINE LXT821

### Spread Spectrum Digital Cordless Telephone Transceiver

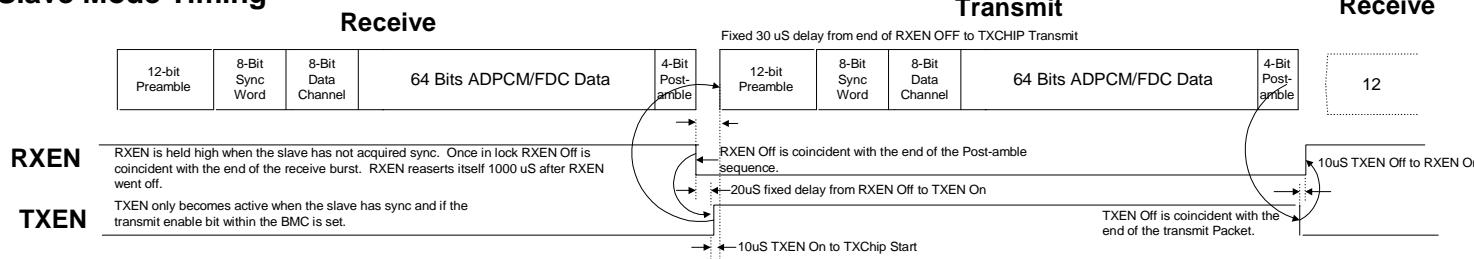

#### 7.5.2 BMC TDD Frame Format – short packet mode

The BMC uses the TDD frame format shown in Figure 21 when set to short packet mode (TXFRMT[6] and RXFRMT[6] set to 1). This feature allows the chip to save power in standby mode.

#### Master Mode Timing

#### Slave Mode Timing

Figure 21 TDD Frame Format of BMC (short packet mode)

## ALPINE LXT821

### Spread Spectrum Digital Cordless Telephone Transceiver

#### 7.5.3 Master/Slave TDD Timing

Master / Slave programming of the BMC is set by **TXFRMT[7]**. When **TXFRMT[7]** = 1, the BMC is programmed for Master timing. When **TXFRMT[7]** = 0, the BMC operates in Slave mode.

The Master/Slave protocol of the BMC is as follows: In Master mode, the BMC transmits TX slots every 2 mS, switching to receive to listen for incoming RX slots between outgoing TX slots.. The Master will transmit TX slots regardless of whether incoming RX slots are received, and the timing of the TX slot is independent of the arrival time of RX slots.

In Slave mode, the BMC stays in receive mode until it has acquired sync, at which point it begins transmitting TX slots back to the Master with a single TX frame, and returns to receive mode. A Slave will continue to respond with TX frames until frame sync is lost.

##### 7.5.3.1 Master Timing Mode

In Master timing mode, all TX timing is derived from the free-running 24 MHz crystal clock. The TX frame is set up as follows:

1. Assuming that TX is enabled (**TXFRMT[4,3]** = 00), the transmit enable line TXEN is asserted at the beginning of a TDD frame.

2. The 96-bit TX slot is output at TXCHIP starting 10 uS after TXEN is asserted.

3. TXEN then goes low after 96 bits have been transmitted, coincident with the end of the last bit cell (970uS after the rising edge of TXEN). TXEN stays low for the remaining 1030 uS of the current frame.

4. If the RX enable bit **RXFRMT[4]** = 0, RXEN is asserted 10 uS after TXEN goes low. It remains high while the RX framer is searching for frame sync. If RX frame sync is found, RXEN remains high until the end of the last received bit cell of the 96-bit RX frame. If sync is not acquired, RXEN returns to low 300 uS after the rising edge. **Errata: In the LXT821A1 and LXT821B1, RXEN does not shorten to 300us if the master unit does not acquire sync.**

5. If TX is still enabled, the sequence is restarted by asserting TXEN again 2000uS after the previous rising edge.