### APPENDIX 6

#### ALIGNMENT INSTRUCTIONS

FIVE (5) PAGES OF ALIGNMENT INSTRUCTIONS FOLLOWS THIS SHEET

ALIGNMENT INSTRUCTIONS FCC ID: MGPNR-150

APPENDIX 6

#### TRANSMITTER ALIGNMENT

Note: Unless otherwise specified, adjust Mic Gain control on the front panel to fully clockwise position for all following tests.

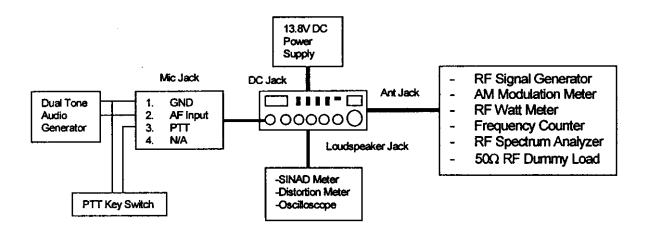

#### A. Test Set-Up

Set up test equipment with the NR-150 radio as indicated below:

#### B. SSB Balanced Modulator Adjustment

- 1. Set the mode selector to USB, and the channel select to CH 20.

- 2. Adjust Mic Gain control on the front panel to minimum (fully counterclockwise)

- 3. Press PTT to transmit on SSB without modulation

- 4. Adjust VR7 for minimum RF output.

- Check RF output on LSB is also minimum

- 6. Resume Mic Gain control to maximum setting (fully clockwise)

#### C. RF Power Transistor Bias Current Adjustment

- Set the mode selector to USB, and the channel select to CH 20.

- 2. Remove the short link PCB (installed vertically in front of the RF Power transistors)

- 3. Connect 100mA FS DC current meter to TP-9 [+] and TP-8 [-].

- Adjust <u>VR11</u> for 60mA ± 3mA to <u>TR44</u>.

- 5. Connect 200mA FS DC current meter to TP-9 [+] and TP-7 [-].

- Adjust <u>VR10</u> to 100mA ± 5mA to <u>TR43</u>.

- Install the short link PCB back to the holder of TP-7, TP-8 & TP-9 upon completion of adjustment.

#### D. AM RF Power Output Adjustment

- Set mode selector to AM.

- Select the channel selector to CH-20.

- 3. Press PTT to transmit.

- 4. Adjust VR-13 for 4W RF Power output. (Without modulation)

#### E. RF Power Amplifier Adjustment

- IMPORTANT: VR-12 Bias adjustment, should not be rotated clockwise beyond 2 o'clock position, otherwise the RF transistor may be destroyed.

- Set the Mode Selector to USB. Compandor OFF.

- 2. Apply 1KHz 50mV RMS audio signal to Microphone input connector pin 2.

- Set the Channel Selector to CH-20.

- 4. Press PTT to transmit.

- Adjust <u>VR-12</u> and <u>L-42</u> for Maximum RF power output as read on the RF Watt Meter.

- 6. Adjust L-40, L-43, L-44 and L-33 for max. RF power output.

- 7. Repeat step 4 to 5 until no further improvement is obtained.

- 8. Adjust <u>L-42</u> for balanced RF Power output on CH40 & CH1.

- Switch to AM Mode, disable audio signal generator, press PTT to transmit.

- 10. Adjust VR-13 for 4W RF Power output on AM Mode with no modulation.

- 11. Switch back to USB Mode, apply 50mV 1KHz audio, press PTT to transmit.

- 12. Switch VSWR meter to Peak Detection Mode.

- 13. Adjust VR-12 for max. 12W SSB Peak Power Output.

#### F AM Modulation Adjustment

- 1. Apply 1KHz 50mV rms. AF signal to Microphone input connector pin 2.

- Activate PTT to transmit in AM Mode. Compandor OFF. Adjust VR-14 for 90% modulation.

- G Compandor Functional Test Transmitter

- Apply 1KHz 2mV rms. AF signal to Microphone input connector pin 2.

- Activate PTT to transmit in AM Mode. Compandor OFF.

- Observe modulation level between 20-80%.

- 4. Switch Compandor to ON

- 5. Observe the modulation level increases to around 90%.

- Increase signal generator level from 2mV to 100mV, Compandor ON.

- Observe the modulation level remains to be less than 100%.

#### H. Advanced Test Procedures for Modulation

Following advanced test procedure requires optional/advanced test equipment setup by experienced technical person, and is not normally required in a field repair environment.

- i) AM Modulation Monitor

- Apply 1KHz 50mV rms. AF signal to Microphone input connector pin 2 of the radio, and to the Y input (Usually marked as Timebase) of the oscilloscope.

- Monitor RF output waveform with X input (usually marked as CH1) of the oscilloscope.

- Activate PTT to transmit on AM Mode. Compandor OFF.

- Confirm the AM Modulation displayed in the oscilloscope is less than 100% as in Fig iA.

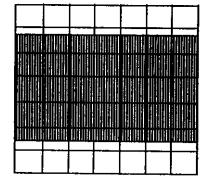

FIG iA - AM Modulation Monitor

Modulation Level = (a-b) x 100% ÷ (a+b) a

FIG iB - No Modulation

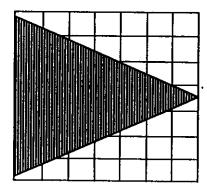

FIG iC - 100% Modulation

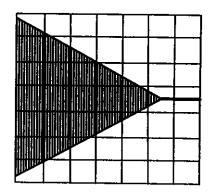

FIG iD - Over Modulation > 100%

- ii) SSB Modulation Monitor

- Use two AF signal generator connected in a star resistor network to provide a balanced 3 input/output ports with impedance of 600Ω. Compandor OFF.

- Apply 500Hz and 2.4KHz 30mV audio tones signals simultaneously through the resistor network to the Microphone input connector pin 2. Activate PTT to transmit on USB Mode.

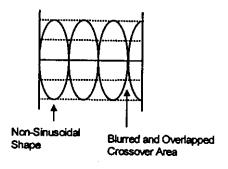

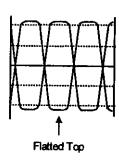

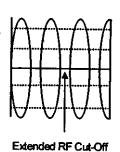

- Adjust the output level of the 500Hz AF signal generator to obtain the proper waveform on the oscilloscope as shown in figure iiA. (See Fig C to D for waveforms of improperly set up radios)

Figure iiA PROPERLY ADJUSTED SSB TRANSMITTER

Sine Wave Shaped Sharp Crossover

At Zero Point

Figure iiB UNBALANCED INPUT TONES

Figure iiC OVER MODULATION

Figure iiD RF POWER TRANSISTORS BIASED INCORRECTLY.

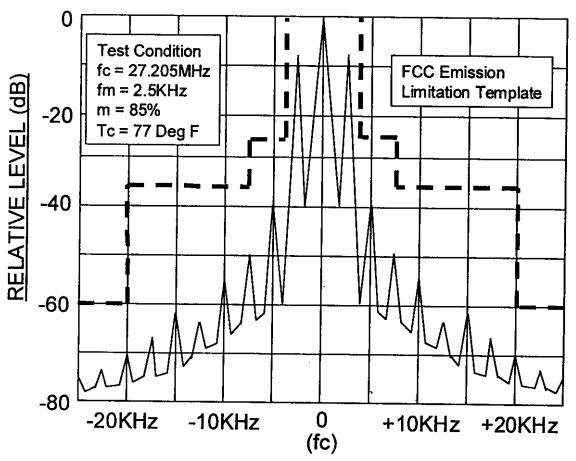

- iii) FCC Emission Limitation Check

- Set up equipment as in i) AM Modulation Monitor Test, Compandor OFF.

- Couple the Spectrum Analyzer input to the RF Dummy Load

- Apply 2.5KHz 50mV rms. audio tones signal to the Microphone input connector pin 2.

- Activate PTT to transmit on AM Mode, adjust AM Modulation level to 85% (see Fig iA).

- Observe on the Spectrum Analyzer that the Radio's RF output are within the FCC limits

- Repeat test with Compandor ON.

### 85% MODULATION SPECTRUM EMISSION LIMITATION TEST

SPREAD FROM CENTER FREQUENCY fc (KHz)

FCC ID: MGPNR-150

#### APPENDIX 7

#### CIRCUITS AND DEVICES TO STABILIZE FREQUENCY

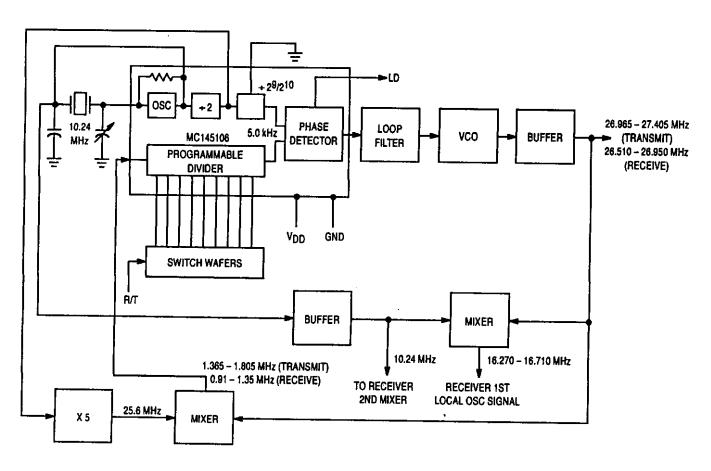

All 40 channels of transmitting, and receiving, frequencies are provided by PLL (Phase Locked Loop) (IC707) circuitry.

The purpose of the PLL is to provide a multiple number of frequencies from a VCO (Voltage Controlled Oscillator) with quartz crystal accuracy and stability locked to crystal oscillator reference frequency.

The reference crystal oscillator frequency is 10.24 MHz.

CIRCUITS AND DEVICES TO STABILIZE FREQUENCY FCC ID: MGPNR-150

FCC ID: MGPNR-150

#### APPENDIX 8

#### A. Circuits For Suppression Of Spurious Radiation

The tuning circuit between the output of final amp TR43 and antenna, 4-stage "Phi" network associated with L34, L51, L52 and L31 serves as a spurious radiation suppressor. This network also serves to match the impedance between TX power amp and the antenna.

#### B. Circuits For Limiting Modulation

Input from the microphone is controlled by the Mic-Gain potentiometer VR505 and amplified by IC4. The amplified signal is used to drive the AM Modulator circuit consists of TR49 & 51.

There are two signals at the base of TR49, the DC voltage controlled by VR13 (RF Power Level Adjust), and the AF level from pin 1 of IC4. The DC bias controls the operating point of the Darlington pair transistors TR50 & 51 to provide power supply to the RF Power transistors TR43 & 44, which controls the RF Carrier Power output of the radio. The AF signal is amplified and superimposed on the DC bias to create high level AM Modulation in TR43 & 44.

The maximum modulation is regulated by the Automatic Level Control (ALC) circuit consists of TR53, TR34 and TR32.

TR53 is a comparator circuit with setpoint adjusted by VR14. When TR53 conducts, the signal is half wave rectified by D83 to drive the current amplifier TR34, which in turn drives TR32 on and shunt down the Mic Audio signal at the input of IC4. The RC circuit (C135, R176 ~ 178) at the base of TR32 ensures the smooth operation of the ALC.

When the modulator overmodulates, AC voltages at emitter of TR53 will increase, and TR53 will conduct more during the negative cycle of the modulation signal, which increases the collector current of TR53 and turn TR43/TR32 on. The audio signal is shunted, input to the modulator decreases until it reaches the Modulation Limit set point of VR14.

#### C. <u>Circuits For Limiting Power</u>

After being amplified by IC4, audio signals from the microphone is connected to the balanced modulator IC3 (pin 1). Signal from the second offset oscillator is presented to pin 3 of IC3 to produce the double side band suppressed carrier (DSBSC) signal. VR7 is adjusted for minimum carrier output.

FCC ID: MGPNR-150

#### C. <u>Circuits For Limiting Power</u> (continued)

The DSBSC signal is routed by the switching diodes to the 10.695 MHz crystal filter, the unwanted sideband is filtered off, and the processed SSB signal is sent to L44/IC9 for mixing with the VCO output (at L43) to obtain the final transmitting frequency.

The high level modulator TR50 & 51 are bypassed by TR52 during SSB operation. The RF Power amplifiers are biased to class B operation (VR10 ~ 11) to preserve the envelope of the low-level modulated SSB signal. Since the SSB RF output is directly proportional to the level of audio signal driving the balanced modulator, the RF output is sampled by TR47, which provides negative feedback to the audio ALC circuit (TR34 & 53) to limit the maximum SSB power output.

DEVICES AND CIRCUITS TO SUPPRESS SPURIOUS RADIATION; LIMIT MODULATION AND POWER FCC ID: MGPNR-150

#### APPENDIX 9

#### PLL DATA SHEETS

FIVE (5) PAGES FOR MC145106 FOLLOW THIS SHEET

COPY OF PLL DATA SHEETS FCC ID: MGPNR-150

APPENDIX 9

# PLL Frequency Synthesizer CMOS

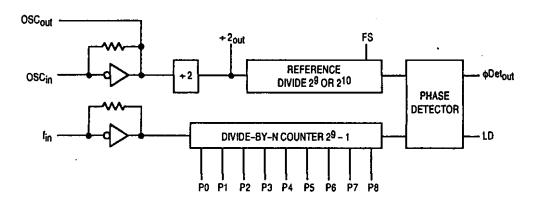

The MC145106 is a phase-locked loop (PLL) frequency synthesizer constructed in CMOS on a single monolithic structure. This synthesizer finds applications in such areas as CB and FM transceivers. The device contains an oscillator/amplifier, a 210 or 211 divider chain for the oscillator signal, a programmable divider chain for the input signal, and a phase detector. The MC145106 has circuitry for a 10.24 MHz oscillator or may operate with an external signal. The circuit provides a 5.12 MHz output signal, which can be used for frequency tripling. A 29 programmable divider divides the input signal frequency for channel selection. The inputs to the programmable divider are standard ground-to-supply binary signals. Pull-down resistors on these inputs normally set these inputs to ground enabling these programmable inputs to be controlled from a mechanical switch or electronic circuitry.

The phase detector may control a VCO and yields a high level signal when input frequency is low, and a low level signal when input frequency is high. An out-of-lock signal is provided from the on-chip lock detector with a "0" level for the out-of-lock condition.

- Single Power Supply

- Wide Supply Range: 4.5 to 12 V

- · Provision for 10.24 MHz Crystal Oscillator

- 5.12 MHz Output

- Programmable Division Binary Input Selects up to 29

- On-Chip Pull-Down Resistors on Programmable Divider Inputs

- Selectable Reference Divider, 2<sup>10</sup> or 2<sup>11</sup> (Including + 2)

- · Three-State Phase Detector

- See Application Note AN535 and Article Reprint AR254

- Chip Complexity: 880 FETs or 220 Equivalent Gates

- See the MC145151-2 and MC145152-2 for Higher Performance and Added Flexibility

#### MC145106

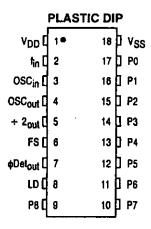

P SUFFIX PLASTIC DIP CASE 707

DW SUFFIX SOG PACKAGE CASE 751D

#### ORDERING INFORMATION

MC145106P MC145106DW Plastic DIP SOG Package

#### **BLOCK DIAGRAM**

#### **PIN ASSIGNMENTS**

#### **SOG PACKAGE**

NC = NO CONNECTION

#### MAXIMUM RATINGS (Voltages Referenced to VSS)

| Parameter                   | Symbol           | Value                          | Unit |

|-----------------------------|------------------|--------------------------------|------|

| DC Supply Voltage           | V <sub>DD</sub>  | 0.5 to + 12                    | V    |

| Input Voltage, All Inputs   | Vin              | - 0.5 to V <sub>DD</sub> + 0.5 | V    |

| DC Input Current, per Pin   | 1                | ±10                            | mA   |

| Operating Temperature Range | TA               | - 40 to + 85                   | °C   |

| Storage Temperature Range   | T <sub>stg</sub> | - 65 to + 150                  | °C   |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit. For proper operation it is recommended that  $V_{in}$  and  $V_{out}$  be constrained to the range  $V_{SS} \leq (V_{in}$  or  $V_{out}) \leq V_{DD}$ .

ELECTRICAL CHARACTERISTICS (TA = 25°C Unless Otherwise Stated, Voltages Referenced to VSS)

|                                                     | <b>AL</b> |                   | V <sub>DD</sub> |              | All Types     |              | _        |

|-----------------------------------------------------|-----------|-------------------|-----------------|--------------|---------------|--------------|----------|

| Characteristic                                      |           | Symbol            | Vdc             | Min          | Тур*          | Max          | Մո       |

| Power Supply Voltage Range                          |           | V <sub>DD</sub>   |                 | 4.5          | _             | 12           | V        |

| Supply Current                                      | A.        | םם <sup>ו</sup>   | 5.0<br>10       |              | 6             | 10           | m        |

|                                                     |           |                   | 12              |              | 20<br>28      | 35<br>50     |          |

| Input Voltage                                       | "0" Level | VIL               | 5.0             | <u> </u>     | <del></del>   | 1.5          | + ,      |

|                                                     | <b></b>   | ' L               | 10              | _            | _             | 3.0          | <b>'</b> |

| •                                                   |           |                   | 12              | _            | -             | 3.6          | -        |

|                                                     | "1" Level | VIH               | 5.0             | 3.5          |               | <b>—</b> —   | 7        |

|                                                     |           | 1                 | 10              | 7.0          |               | l –          |          |

|                                                     |           |                   | 12              | 8.4          |               |              |          |

| nput Current                                        | "0" Level | l <sub>in</sub>   | 5.0             | - 5.0        | - 20          | - 50         | μ/       |

| FS, Pull-Up Resistor Source Current)                |           | ] }               | 10              | - 15         | -60           | - 150        |          |

| 49a - Fai                                           |           | i I               | 12              | - 20         | - 80          | - 200        |          |

| (P0 – P8)                                           |           |                   | 5.0             |              |               | - 0.3        |          |

|                                                     |           | [ ]               | 10              | i –          | -             | -0.3         | 1        |

| (50)                                                |           |                   | 12              |              |               | -0.3         | _]       |

| (FS)                                                | "1" Level |                   | 5.0             | -            | -             | 0.3          |          |

|                                                     |           |                   | 10<br>12        | ] =          |               | 0.3<br>0.3   |          |

| (P0 - P8, Pull-Down Resistor Sink Current)          |           | <b> </b>          |                 | <del> </del> | <del></del>   | ·            | 4        |

| ( C C C) - Si Domi rediciol Crix Odlient)           |           |                   | 5.0<br>10       | 7.5<br>22.5  | 30<br>90      | 75           | 1        |

|                                                     |           |                   | 12              | 30           | 120           | 225<br>300   | 1        |

| (OSC <sub>in</sub> , f <sub>in</sub> )              | "0" Level | -                 | 5.0             | - 2.0        | <del></del>   |              | -        |

|                                                     |           | . (               | 10              | -6.0         | - 6.0<br>- 25 | - 15<br>- 62 |          |

|                                                     | ,         |                   | 12              | - 9.0        | - 37          | - 92         |          |

| (OSC <sub>in</sub> , f <sub>in</sub> )              | "1" Level | <u> </u>          | 5.0             | 2.0          | 6.0           | 15           | ┥        |

|                                                     |           |                   | 10              | 6.0          | 25            | 62           | 1        |

|                                                     |           |                   | 12              | 9.0          | 37            | 92           |          |

| Output Drive Current                                |           | ЮН                |                 |              |               |              | m/       |

| $(V_O = 4.5 \text{ V})$<br>$(V_O = 9.5 \text{ V})$  | Source    |                   | 5.0             | - 0.7        | -1.4          | ( –          | ""       |

| $(V_0 = 3.5 \text{ V})$<br>$(V_0 = 11.5 \text{ V})$ |           |                   | 10              | -1.1         | -2.2          | -            |          |

|                                                     |           |                   | 12              | - 1.5        | - 3.0         |              | _        |

| $(V_O = 0.5 V)$<br>$(V_O = 0.5 V)$                  | Sink      | lOL               | 5.0             | 0.9          | 1.8           |              | ]        |

| $(V_0 = 0.5 \text{ V})$                             |           | ļ                 | 10<br>12        | 1.4<br>2.0   | 2.8           | -            |          |

| put Amplitude                                       |           |                   | 12              | 2.0          | 4.0           |              |          |

| (fin @ 4.0 MHz)                                     | 1         | -                 |                 | 1.0          | 0.0           |              | V p-     |

| (OSC <sub>In</sub> @ 10.24 MHz)                     |           |                   |                 | 1.5          | 0.2<br>0.3    | _            | Sine     |

| put Resistance                                      |           | Rin               |                 |              |               |              | <u> </u> |

| (OSC <sub>in</sub> , f <sub>in</sub> )              | i         |                   | 5.0             | _            | 1.0           | _            | МΩ       |

|                                                     |           |                   | 10              |              | 0.5           | _            | ĺ        |

|                                                     |           |                   | 12              | _            | -             | <b>–</b>     |          |

| put Capacitance                                     |           | Cin               |                 |              | 6.0           |              | pF       |

| (OSC <sub>in</sub> , f <sub>in</sub> )              |           |                   | ĺ               |              |               |              | [        |

| ree-State Leakage Current                           |           | loz               | 5.0             |              |               | 1.0          | 11 A     |

| (¢Det <sub>out</sub> )                              | ĺ         |                   | 10              | _            |               | 1.0          | μА       |

|                                                     |           |                   | 12              | - 1          | - 1           | 1.0          | •        |

| out Frequency                                       |           | fin               | 4.5             | 0            |               | 4.0          | MHz      |

| (- 40 to + 85°C)                                    |           |                   | 12              | o l          | _ }           | 4.0          | 41112    |

| cillator Frequency                                  |           | osc <sub>in</sub> | 4.5             | 0.1          |               | 10.24        | A 40 t=  |

| (− 40 to + 85°C)                                    | 1         | - ""              | 12              | 0.1          | _             | 10.24        | MHz      |

<sup>\*</sup>Data labelled "Typ" is not to be used for design purposes but is intended as an indication of the IC's potential performance.

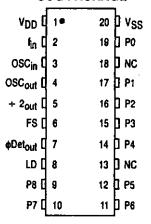

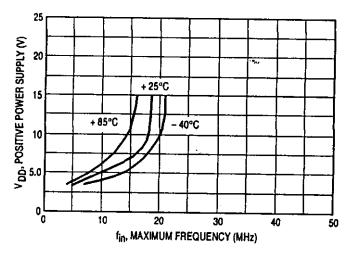

#### TYPICAL CHARACTERISTICS\*

25

20 VDD, SUPPLY VOLTAGE (V) + 25°C 15 +85°C - 40°C 10 Ω 10 20 30 40 50 OSCin, MAXIMUM FREQUENCY (MHz)

Figure 1. Maximum Divider Input Frequency versus Supply Voltage

Figure 2. Maximum Oscillator Input Frequency versus Supply Voltage

#### TRUTH TABLE

| Selection |    |    |    |    |     |    |    |       |             |  |  |

|-----------|----|----|----|----|-----|----|----|-------|-------------|--|--|

| P8        | P7 | P6 | P5 | P4 | P3  | P2 | P1 | PO    | Divide by N |  |  |

| 0         | 0  | 0  | 0  | 0  | 0   | 0  | 0  | 0     | 2*          |  |  |

| 0         | 0  | 0  | 0  | 0  | 0   | 0  | 0  | ĺ 1 : | 3*          |  |  |

| 0         | 0  | 0  | 0  | 0  | 0   | 0  | 1  | اها   | 2           |  |  |

| 0         | 0  | 0  | 0  | 0  | 0   | 0  | 1  | 1     | 3           |  |  |

| 0         | 0  | 0  | 0  | 0  | 0   | 1  | 0  | ا ہ ا | 4           |  |  |

| •         |    |    | :  | :  |     | :  | :  |       | :           |  |  |

| 0         | 1  | 1  | 1  | 1  | 1 1 | 1  | 1  |       | 255         |  |  |

| :         | :  | :  | •  | •  | •   |    |    |       | :           |  |  |

| 1         | 1  | 1  | 1  | 1  | 1   | 1  | 1  | 1     | 511         |  |  |

<sup>1:</sup> Voltage level = VDD.

#### PIN DESCRIPTIONS

P0 - P8 Programmable inputs (PDIP -- Pins 17 - 9; SOG -- Pins 19, 17 - 14, 12 - 9)

Programmable divider inputs (binary).

#### fin Frequency Input (PDIP, SOG --- Pin 2)

Frequency input to programmable divider (derived from VCO).

oscin, oscout

Oscillator Input and Oscillator Output (PDIP, SOG ---Pins 3, 4)

Oscillator/amplifier input and output terminals.

#### LD Lock Detector (PDIP, SOG --- Pin 8)

LD is high when loop is locked, pulses low when out-oflock.

####

Signal for control of external VCO, output high when fin/N is less than the reference frequency; output low when fin/N is greater than the reference frequency. Reference frequency is the divided down oscillator — input frequency typically 5.0 or 10 kHz.

#### NOTE

Phase Detector Gain =  $V_{DD}/4\pi$ .

#### Reference Oscillator Frequency Division Select (PDIP, SOG - Pin 6)

When using 10.24 MHz OSC frequency, this control selects 10 kHz, a "0" selects 5.0 kHz.

#### +2<sub>out</sub> (PDIP, SOG — PIn 5)

Reference OSC frequency divided by 2 output; when using 10.24 MHz OSC frequency, this output is 5.12 MHz for frequency tripling applications.

#### $V_{DD}$

Positive Power Supply (PDIP, SOG — Pin 1)

#### Vss Ground (PDIP — Pin 18, SOG — Pin 20)

<sup>\*</sup> Data labelled "Typ" is not to be used for design purposes but is intended as an indication of the iC's potential performance.

<sup>0:</sup> Voltage level = 0 or open circuit input.

<sup>\*</sup>The binary setting of 00000000 and 00000001 on P8 to P0 results in a 2 and 3 division which is not in the  $2^{N} - 1$  sequence. When pin is not connected the logic signal on that pin can be treated as a "0".

#### PLL SYNTHESIZER APPLICATIONS

The MC145106 is well suited for applications in CB radios because of the channelized frequency requirements. A typical 40 channel CB transceiver synthesizer, using a single crystal reference, is shown in Figure 3 for receiver IF values of 10.695 MHz and 455 kHz.

In addition to applications in CB radios, the MC145106 can be used as a synthesizer for several other systems. Various frequency spectrums can be achieved through the use of proper offset, prescaling, and loop programming techniques. In general, 300 – 400 channels can be synthesized using a single loop, with many additional channels available when multiple loop approaches are employed. Figures 4 and 5 are examples of some possibilities.

In the aircraft synthesizer of Figure 5, the VHF loop (top) will provide a 50 kHz, 360 channel system with 10.7 MHz R/T offset when only the 11.0500 MHz (transmit) and

12.1200 MHz (receive) frequencies are provided to mixer #1. When these signals are provided with crystal oscillators, the result is a three crystal 360 channel, 50 kHz step synthesizer. When using the offset loop (bottom) in Figure 5 to provide the indicated injection frequencies for mixer #1 (two for transmit and two for receive) 360 additional channels are possible. This results in a 720—channel, 25 kHz step synthesizer which requires only two crystals and provides R/T offset capability. The receive offset value is determined by the 11.31 MHz crystal frequency and is 10.7 MHz for the example.

The VHF marine synthesizer in Figure 4 depicts a single loop approach for FM transceivers. The VCO operates on frequency during transmit and is offset downward during receive. The offset corresponds to the receive IF (10.7 MHz) for channels having identical receive/transmit frequencies (simplex), and is (10.7-4.6=6.1) MHz for duplex channels. Carrier modulation is introduced in the loop during transmit.

Figure 3. Single Crystal CB Synthesizer Featuring On-Frequency VCO During Transmit

#### APPENDIX 10

#### FINAL RF AMPLIFIER DATA SHEETS

THREE (3) PAGES FOR 2SC1969 FOLLOW THIS SHEET

FINAL RF AMP DATA SHEET FCC ID: MGPNR-150

### C.B. Mobile Transceiver

2SC1969

**TR-43**

NPN EPITAXIAL PLANAR TYPE

#### DESCRIPTION

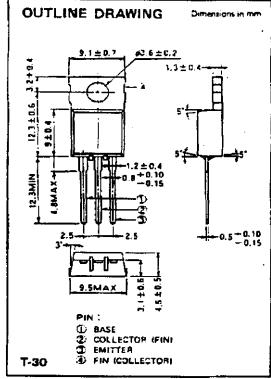

2SC1969 is a silicon NPN epitaxial planar type transistor designed for RF power amplifiers on HF band mobile radio applications.

#### **FEATURES**

- High power gain: G<sub>De</sub> ≥ 12d8

@V<sub>CC</sub> = 12V, P<sub>G</sub> = 16W, f = 27MHz

- Emitter ballasted construction for high reliability and good performances.

- TO-220 package similarly is combinient for mounting.

- Ability of withstanding infinite load VSWR when operated at  $V_{CC}$  = 16V,  $P_{O}$  = 20W, f = 27MHz.

#### **APPLICATION**

16 to 14 watts output power class AB amplifiers applications in HF band.

#### ABSOLUTE MAXIMUM RATINGS (To=25°C unless otherwise specified)

| Symbol       | Parameter                    | Conditions            | Patings     | Unit |

|--------------|------------------------------|-----------------------|-------------|------|

| <b>V</b> cac | Collector to base voltage    |                       | 60          | V    |

| VEBC         | Emister to base voltage      |                       | 5           | V    |

| VCEO         | Collector to emitter voltage | Agg ≈ ∞               | 25          | V    |

| ic           | Collector current            |                       | Б           | A    |

| Pc           | Collector desipation         | T <sub>6</sub> = 25°C | 1.7         | w    |

|              |                              | Te = 25°C             | 20          | w    |

| Τį           | Junction temperature         |                       | 150         | ٠.   |

| Tatg         | Storage temperature          |                       | - 55 to 150 | °c   |

| Ath-a        |                              | Junction to amplynt   | 73.5        | ·c/w |

| Ptn-c        | Thermal resistance           | Junction to case      | 8.25        | 'c/w |

Note: Adove carameters are guaranteed independently

#### ELECTRICAL CHARACTERISTICS (To = 25°C unless otherwise specified)

| Symbo.   | Farameter                              | Test conditions                           | Limits |           |       |      |

|----------|----------------------------------------|-------------------------------------------|--------|-----------|-------|------|

|          |                                        | Tast Conditions                           | Min    | Tyc       | Max   | Unit |

| V(BP)EBC | Emitter to base breakdown voitage      | 1€ = \$#A. 1€ = 0                         | 5      |           |       | V    |

| V(BR)CBC | Collector to best breakdown voltage    | tc=1mA, l <sub>E</sub> =€                 | 60     | · · · · · |       | v    |

| VIBRICES | Collector to emitter breakdown voltage | IC-10mA, ABE                              | 25     |           |       | v    |

| 'cac     | Sallector cutoff current               | V <sub>CB</sub> → 30V, I <sub>E</sub> = 0 |        |           | 100   | Aμ   |

| 1200     | Emitter cutoff cuirgn;                 | VEB-4V, IC-0                              |        |           | 100 - | ∆ير  |

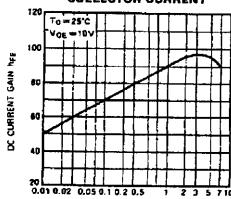

| yes      | DC forward current pain.*              | Vcg =12V. 1c =10mA                        | 10     | \$0       | 180   |      |

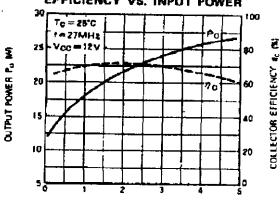

| Po       | Quipot power                           |                                           | 16     | 1.8       | 1     | w    |

| 7c       | Consistor efficiency                   | Vcc=12V. Pin=1w , f=27MHz                 | · 60   | 70        | 1     | %    |

Rise: a Pulse rect: Pwik 150 µs; duty=5%.

Above parameters, ratings, whits and conditions are subject to change

| ٠, |      |       |       |       |        |        |  |

|----|------|-------|-------|-------|--------|--------|--|

| -  | Item | ×     | 4     | e     | C      | D      |  |

|    | ueē  | 10-25 | 20-45 | 35-7D | 55-110 | 90-180 |  |

# **Parts Specification**

Page 2/3

### C.B. Mobile Transceiver

2SC1969

NPN EPITAXIAL PLANAR TYPE

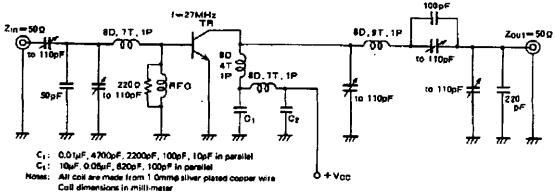

#### TEST CIRCUIT

D: Inner diameter of coil T: Turn number of coil

P: Pitch of coil

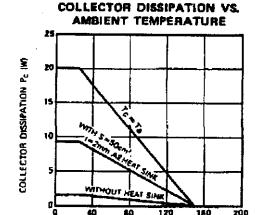

#### 'PICAL PERFORMANCE DATA

AMBIENT TEMPERATURE To ("C)

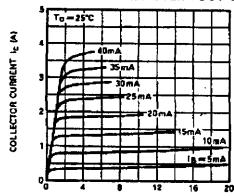

### COLLECTOR CURRENT VS. COLLECTOR TO EMITTER VOLTAGE

COLLECTOR TO EMITTER VOLTAGE VCE (V)

### OC CURRENT GAIN VS.

COLLECTOR CURRENT IC (A)

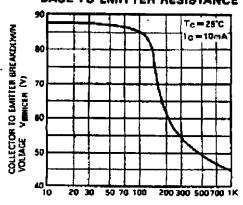

#### COLLECTOR TO EMITTER BREAKDOWN VOLTAGE VS. BASE TO EMITTER RESISTANCE

BASE TO EMITTER RESISTANCE Res (Q)

# **Parts Specification**

Page 3/3

### C.B. Mobile Transceiver

2SC1969

NPN EPITAXIAL PLANAR TYPE

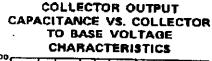

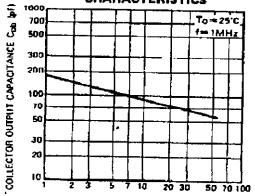

COLLECTOR TO BASE VOLTAGE VCB IVI

### OUTPUT POWER, COLLECTOR EFFICIENCY VS. INPUT POWER

INPUT POWER Pin (W)

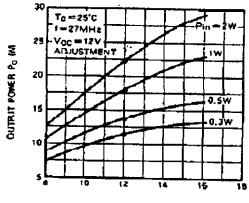

#### OUTPUT POWER VS. COLLECTOR SUPPLY VOLTAGE

COLLECTOR SUPPLY VOLTAGE V. [V]

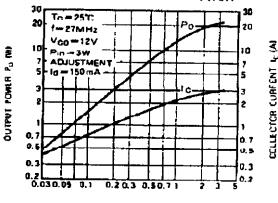

#### IN CASE AB OPERATING OUTPUT POWER COLLECTOR CURRENT VS. INPUT POWER

INPIT POWER P. (W)

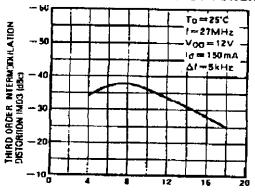

### THIRD ORDER INTERMODULATION DISTORTION V5. OUTPUT POWER

OUTPUT POWER LEVEL (PEP) (W)