**RDA Series

Reference Manual**

**T a b l e   o f   C o n t e n t s**

|         |                                            |    |

|---------|--------------------------------------------|----|

| 1       | Introduction .....                         | 3  |

| 2       | General Information .....                  | 4  |

| 2.1     | Specification.....                         | 6  |

| 2.1.1   | RDA Specification .....                    | 6  |

| 2.1.2   | RDA2 Specification .....                   | 7  |

| 2.2     | Pinout Description .....                   | 8  |

| 2.3     | Mechanical Description .....               | 9  |

| 2.4     | Antenna Connection .....                   | 9  |

| 3       | Theory of Operation .....                  | 10 |

| 3.1     | Transmitter Operation .....                | 12 |

| 3.2     | Receiver Operation .....                   | 12 |

| 3.3     | Synthesizer .....                          | 13 |

| 3.4     | TX/RX Line .....                           | 13 |

| 3.5     | STANDBY .....                              | 13 |

| 3.6     | RSSI .....                                 | 14 |

| 4       | Operation .....                            | 14 |

| 4.1     | Overview .....                             | 14 |

| 4.2     | Parallel Interface Overview .....          | 15 |

| 4.2.1   | Register Descriptions .....                | 18 |

| 4.2.2   | Bus Timing Diagrams .....                  | 22 |

| 4.3     | Radio Control .....                        | 23 |

| 4.3.1   | Frequency Programming .....                | 23 |

| 4.3.2   | Transmit Mode .....                        | 27 |

| 4.3.2.1 | From Standby Mode .....                    | 28 |

| 4.3.2.2 | From Receive Mode .....                    | 28 |

| 4.3.2.3 | From Transmit Mode .....                   | 29 |

| 4.3.3   | Receive Mode .....                         | 30 |

| 4.3.3.1 | From Standby Mode .....                    | 30 |

| 4.3.3.2 | From Tranmit Mode .....                    | 31 |

| 4.3.3.3 | From Receive Mode .....                    | 32 |

| 4.3.4   | Standby Mode .....                         | 32 |

| 4.3.4.1 | From Transmit Mode .....                   | 33 |

| 4.3.4.2 | From Receive Mode .....                    | 33 |

| 4.3.5   | Radio Timing Chart .....                   | 33 |

| 4.4     | Data Interface Timing .....                | 34 |

| 5       | Performance Verification Testing .....     | 37 |

| 5.1     | Equipment List .....                       | 37 |

| 5.2     | Equipment Setup .....                      | 38 |

| 5.3     | Main Performance Tests .....               | 39 |

| 5.3.1   | Power Output .....                         | 39 |

| 5.3.2   | Bit Error Rate (BER) .....                 | 39 |

| 5.3.3   | Sensitivity .....                          | 39 |

| 5.3.4   | Dynamic Range .....                        | 40 |

| 5.3.5   | Carrier Frequency .....                    | 40 |

| 5.3.6   | Modulation BW .....                        | 40 |

| 5.3.7   | Processing Gain .....                      | 40 |

| 5.3.8   | Data Clock Rate .....                      | 40 |

| 5.3.9   | Emmission outside (902-928) MHz band ..... | 40 |

| 5.3.9.1 | Harmonic Distortion .....                  | 40 |

| 5.3.9.2 | Leakage .....                              | 40 |

|         |                                                     |     |

|---------|-----------------------------------------------------|-----|

| 5.3.10  | Power Consumption .....                             | 4 1 |

| 5.4     | Supplementary Characteristics Test .....            | 4 1 |

| 5.4.1   | Undesired Signal Rejection .....                    | 4 1 |

| 5.4.1.1 | Adjacent Channel Rejection .....                    | 4 1 |

| 5.4.1.2 | Interference Rejection .....                        | 4 1 |

| 5.4.1.3 | Image Rejection .....                               | 4 1 |

| 5.4.2   | Receiver Turn-on Time .....                         | 4 2 |

| 5.4.3   | Transmitter Turn-on Time .....                      | 4 2 |

| 5.4.4   | Transmitter Turn-off Time .....                     | 4 2 |

| 5.4.5   | Receiver Turn-on Time .....                         | 4 2 |

| 5.4.6   | RSSI .....                                          | 4 2 |

|         | Addendum A-Vbat vs. Power Out and Ibat Graphs ..... | 4 3 |

## 1 Introduction

This manual describes the installation and operation of the Proxim RDA series radios: the RDA (100-300 mW, 121 Kbps) and the RDA2 (100-300 mW, 242 Kbps). In the following sections, the major issues associated with integrating the radio within a system and establishing communication between radios are covered. In addition, a means to test the performance of the radio is described.

This document consists of four major sections: 2) *General Information*, 3) *Theory of Operation*, 4) *Operation* and 5) *Performance Verification Testing*. *General Information* details the radio specifications and the physical characteristics of the radio board. *Theory of Operation* introduces the primary functional components of the radio and their impact on operation. *Operation* describes the exact procedures to be followed in order to achieve successful communication between radios. *Performance Verification Testing* offers a detailed technique for testing the radio to ensure it complies to its specifications.

Proxim reserves the right to make changes without notice to any products herein for any reason at any time, including but not limited to improving the reliability, form, fit, function or design. Proxim does not assume any liability arising out of use, misuse or application of any product or circuit described herein, nor does it convey any license under its patent rights nor the rights of others.

Proxim products are not designed, intended or authorized for use in life support applications or any other application which the failure of the Proxim product could result in personal injury or death. Should Buyer purchase or use Proxim products for any unintended or unauthorized application, Buyer shall indemnify and hold Proxim harmless against all claims, costs, damages and expenses arising out of, directly or indirectly, claims for personal injury and death from said use, even if negligent design or manufacture is claimed.

Information and specifications in this manual are checked, however no responsibilities for inaccuracies can be assumed by Proxim. Please consult a Proxim salesperson to obtain the latest specifications before placing your order for Proxim products.

## 2 General Information

Proxim radios are designed to meet FCC regulations on spread spectrum operation as described in part 15.247 of the code of Federal regulations. However, OEM integration of these radios into equipment may affect radio performance.

A one-time equipment certification is granted by FCC for radio equipped final product. As a result, it is the OEM's responsibility to acquire the FCC certification.

The Proxim RDA series radios are a line of miniature, low power, single board, spread spectrum radio transceivers. This family operates in the 902-928MHz ISM band which has been assigned by the Federal Communications Commission (FCC) for unlicensed use by spread spectrum systems. To help combat any potential interference in this band, the RDA has four independent frequency channels available with full adjacent channel rejection. It also has three additional half channels (seven total) at reduced adjacent channel rejection. The half channels may be used, for example, in alternate cells in a cell-oriented network. The radio is designed to switch channels very rapidly (e.g. for use in repeater or general scanning applications). The RDA2 has three independent frequency channels available with full adjacent channel rejection, since each channel occupies a wider frequency band than those in the RDA.

The RDA series was designed to interface in parallel fashion to a microprocessor bus. The radios have a built-in HDLC controller which implements low level HDLC protocol functions. Since the radio cannot transmit and receive at the same time, it must operate in a half duplex mode. The interface for power, data, and control signals is provided through a 32-pin connector.

All Proxim radios provide a low current Standby mode to simplify power management in applications where power consumption is critical. They also have a carrier detect output signal (CD) that is low when a Proxim compatible spread spectrum signal is present. The received data can be programmed to be gated by this carrier detect signal.

These radios were designed to handle the large range of input signal levels encountered in a dynamic, real-life portable environment. The wide dynamic range allows two radios to operate beside one another, as well as at a distance. An analog Received Signal Strength Indicator (RSSI) output is also provided.

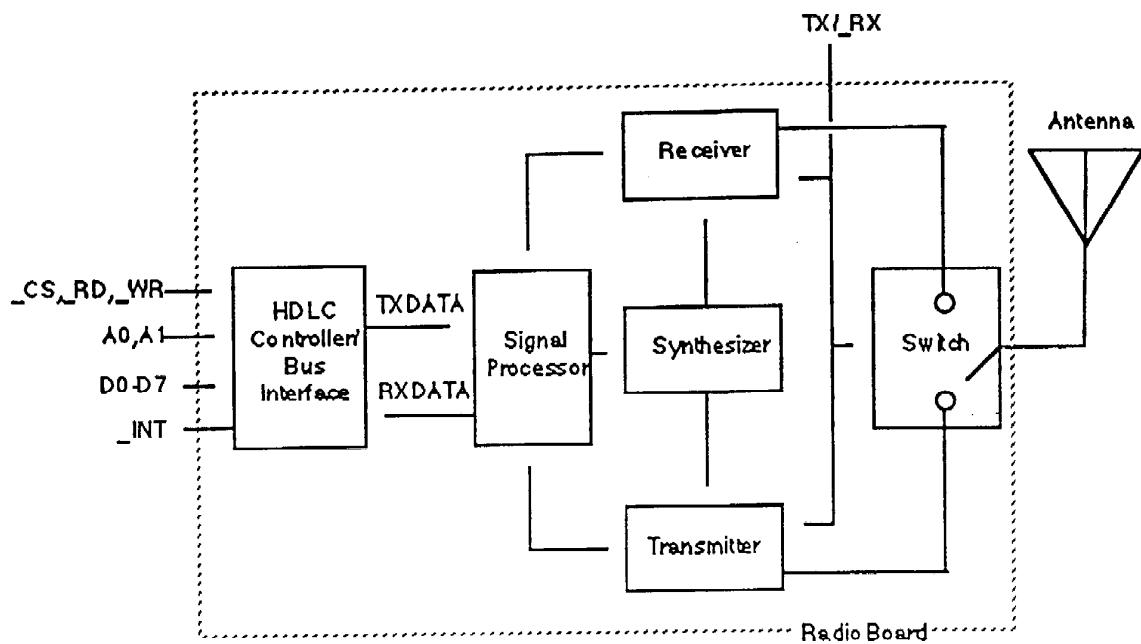

Figure 1 below, is a simplified block diagram of the RDA series radio and illustrates the interaction of the major elements.

Figure 1 - RDA Series Block Diagram

THE RDA SERIES RADIOS CONTAIN

STATIC SENSITIVE DEVICES, AND

THEREFORE, SHOULD BE HANDLED

USING APPROPRIATE ESD

PROCEDURES.

## 2.1 Specifications

### 2.1.1 RDA Specifications

#### General Specifications

|                                              |                                    |

|----------------------------------------------|------------------------------------|

| Output Power .....                           | 100-300 mW                         |

| Sensitivity (@ $1 \times 10^{-5}$ BER) ..... | -95 dBm (typ), -90 dBm (min)       |

| Frequency Band .....                         | 902-928 MHz                        |

| Number of Channels .....                     | 4 full channels (7 half channels)  |

| Frequency Control .....                      | Synthesized, Software Programmable |

| Data Rate .....                              | 121 Kbps                           |

#### Supplemental Performance Characteristics

|                                            |               |

|--------------------------------------------|---------------|

| 1/2 Channel Rejection (3 MHz) .....        | 20 dBc (typ)  |

| Adjacent Channel Rejection (6 MHz) .....   | 55 dBc (typ)  |

| Alternate Channel Rejection (12 MHz) ..... | 60 dBc (typ)  |

| Image Rejection .....                      | 40 dBc (typ)  |

| meets FCC Part 15.247 (spread spectrum)    |               |

| Modulation Bandwidth                       |               |

| -6 dBc .....                               | 1.8 MHz (typ) |

| -40 dBc .....                              | 4.2 MHz (typ) |

#### Timing

|                                    |               |

|------------------------------------|---------------|

| TX turn-on time .....              | 100 $\mu$ sec |

| TX turn-off time .....             | 50 $\mu$ sec  |

| TX-to-RX switching time .....      | 1 msec        |

| RX-to-TX switching time .....      | 1 msec        |

| Power-on time (from Standby) ..... | 5 msec        |

| Frequency switching time .....     | 1 msec        |

#### Power

##### Receive

|            |                                   |

|------------|-----------------------------------|

| 5V .....   | 65 mA (typ), 75 mA (max)          |

| VBAT ..... | 1 $\mu$ A (typ), 20 $\mu$ A (max) |

##### Transmit

|                 |             |

|-----------------|-------------|

| 5V .....        | 65 mA (max) |

| VBAT (9V) ..... | 225 mA      |

##### Standby

|            |                                   |

|------------|-----------------------------------|

| 5V .....   | <200 $\mu$ A                      |

| VBAT ..... | 1 $\mu$ A (typ), 20 $\mu$ A (max) |

##### Operating Voltage Range

|            |              |

|------------|--------------|

| 5V .....   | 4.7V to 5.3V |

| VBAT ..... | 4.5V to 9.0V |

#### Physical Characteristics

|              |                      |

|--------------|----------------------|

| Size .....   | 2.4" x 3.75" x 0.42" |

| Weight ..... | 2 oz.                |

|                                   |                 |

|-----------------------------------|-----------------|

| Operating Temperature Range ..... | 20° C to +60° C |

|-----------------------------------|-----------------|

|                                 |                  |

|---------------------------------|------------------|

| Storage Temperature Range ..... | -50° C to +85° C |

|---------------------------------|------------------|

#### Other Functions

|            |                                    |

|------------|------------------------------------|

| RSSI ..... | Received Signal Strength Indicator |

| CD .....   | Carrier Detect Indicator           |

### 2.1.2 RDA2 Specifications

#### General Specifications

|                                              |                                    |

|----------------------------------------------|------------------------------------|

| Output Power .....                           | 100-300 mW                         |

| Sensitivity (@ $1 \times 10^{-5}$ BER) ..... | -90 dBm (min)                      |

| Frequency Band .....                         | 902-928 MHz                        |

| Number of Channels .....                     | 3 full channels                    |

| Frequency Control .....                      | Synthesized, Software Programmable |

| Data Rate .....                              | 242 Kbps                           |

#### Supplemental Performance Characteristics

|                                            |               |

|--------------------------------------------|---------------|

| Adjacent Channel Rejection (9 MHz) .....   | 50 dBc (typ)  |

| Alternate Channel Rejection (12 MHz) ..... | 60 dBc (typ)  |

| Image Rejection .....                      | 40 dBc (typ)  |

| Modulation Bandwidth                       |               |

| -6 dBc .....                               | 3.6 MHz (typ) |

| -40 dBc .....                              | 8.4 MHz (typ) |

#### Timing

|                                    |               |

|------------------------------------|---------------|

| TX turn-on time .....              | 100 $\mu$ sec |

| TX turn-off time .....             | 50 $\mu$ sec  |

| TX-to-RX switching time .....      | 1 msec        |

| RX-to-TX switching time .....      | 1 msec        |

| Power-on time (from Standby) ..... | 2.5 msec      |

| Frequency switching time .....     | 1 msec        |

#### Power

|                         |                                   |

|-------------------------|-----------------------------------|

| Receive                 |                                   |

| 5V .....                | 85 mA (max)                       |

| VBAT .....              | 1 $\mu$ A (typ), 20 $\mu$ A (max) |

| Transmit                |                                   |

| 5V .....                | 75 mA (max)                       |

| VBAT (9V) .....         | 225 mA                            |

| Standby                 |                                   |

| 5V .....                | <200 $\mu$ A                      |

| VBAT .....              | 1 $\mu$ A (typ), 20 $\mu$ A (max) |

| Operating Voltage Range |                                   |

| 5V .....                | 4.7V to 5.3V                      |

| VBAT .....              | 4.5V to 9.0V                      |

#### Physical Characteristics

|                                   |                      |

|-----------------------------------|----------------------|

| Size .....                        | 2.4" x 3.75" x 0.42" |

| Weight .....                      | 2 oz.                |

| Operating Temperature Range ..... | -20° C to +60° C     |

| Storage Temperature Range .....   | -50° C to +85° C     |

#### Other Functions

|            |                                    |

|------------|------------------------------------|

| RSSI ..... | Received Signal Strength Indicator |

| CD .....   | Carrier Detect Indicator           |

## 2.2 Pinout Description

The radio data/power interface is a 32-pin male connector with 0.025" square posts and 0.1" lead spacing.

### RDA Series Radio Pinout Description

| Pin   | Signal         | Function                                                                                                                                                                                                                                                                                                                                                |

|-------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-8   | D0-D7          | The data pins should be connected to the microprocessor data bus.                                                                                                                                                                                                                                                                                       |

| 9     | <u>RD</u>      | The read pin controls the radio's read operations.                                                                                                                                                                                                                                                                                                      |

| 10    | <u>WR</u>      | The write pin controls the radio's write operations.                                                                                                                                                                                                                                                                                                    |

| 11    | <u>CS</u>      | Chip Select is used to determine the radio's registers.                                                                                                                                                                                                                                                                                                 |

| 12-13 | A1-A0          | The address pins are used for address selection of the registers in the radio's parallel interface section. They should be connected to the microprocessor address bus.                                                                                                                                                                                 |

| 14-16 | NC             | Not connected.                                                                                                                                                                                                                                                                                                                                          |

| 17-18 | GND            | Ground.                                                                                                                                                                                                                                                                                                                                                 |

| 19    | +5V            | +5V supply.                                                                                                                                                                                                                                                                                                                                             |

| 20    | GND            | Ground.                                                                                                                                                                                                                                                                                                                                                 |

| 21    | NC             | Not connected.                                                                                                                                                                                                                                                                                                                                          |

| 22    | GND            | Ground.                                                                                                                                                                                                                                                                                                                                                 |

| 23    | INT            | The interrupt pin should be connected to the microprocessor interrupt line. You MUST pull up _INT with a 10K resistor to +5V on your board. The Interrupt Signal is a Level Sensitivity Signal. When an Interrupt is generated, this signal will remain low until the Interrupt is explicitly cleared by reading or writing to an appropriate register. |

| 24    | <u>CD</u>      | Carrier detect (active low) goes active when a valid carrier is detected. Only carriers encoded with the RDA series spreading code are valid.                                                                                                                                                                                                           |

| 25    | TX/RX          | The transmit/receive line is an input. When high, the radio's transmitter is enabled.                                                                                                                                                                                                                                                                   |

| 26    | GND            | Ground.                                                                                                                                                                                                                                                                                                                                                 |

| 27    | <u>STANDBY</u> | When set low, this input line resets all digital electronics and puts the radio into its low power state.                                                                                                                                                                                                                                               |

| 28    | +5V            | +5V supply.                                                                                                                                                                                                                                                                                                                                             |

| 29    | RSSI           | RSSI (Received Signal Strength Indicator) is an analog output from the demodulator.                                                                                                                                                                                                                                                                     |

| 30    | VBAT           | Output stage +5V supply.                                                                                                                                                                                                                                                                                                                                |

| 31-32 | GND            | Ground.                                                                                                                                                                                                                                                                                                                                                 |

### 2.3 Mechanical Specifications

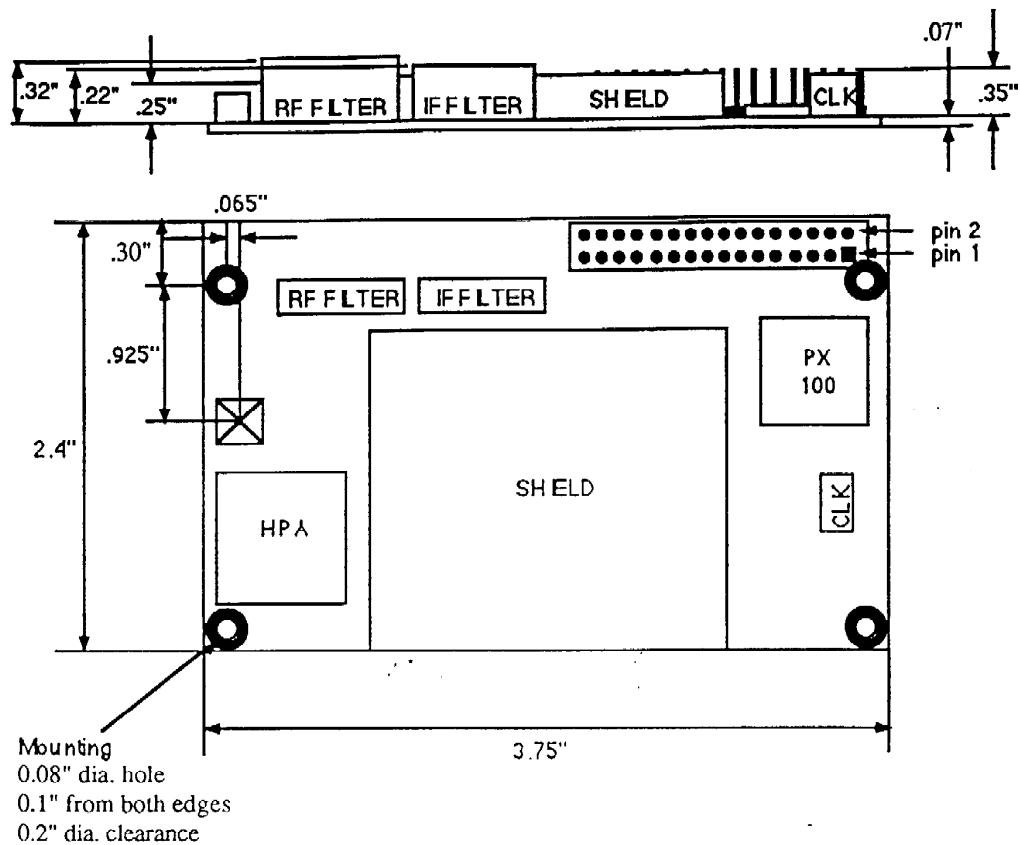

Figure 2 shows the physical dimensions of the RDA and the RDA2 radios.

Figure 2 - RDA and RDA2 Physical Dimensions

### 2.4 Antenna Connection

All Proxim radios include a BFA jack as the antenna interface. Proxim offers BFA compatible cables with an unterminated end.

### 3 Theory of Operation

This section gives an overview of the components in the RDA series radios. It gives insight into the radio's performance. Section 4 details the radio's operation.

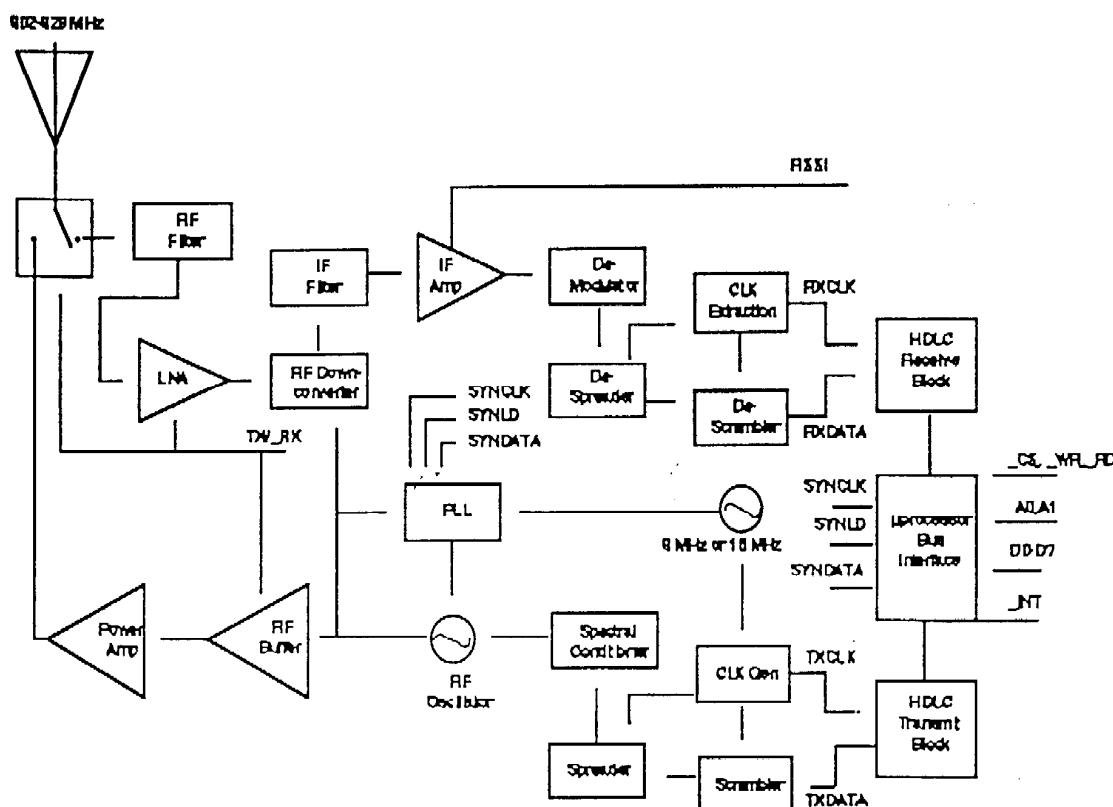

Figure 3 is a block diagram of the RDA series radio.

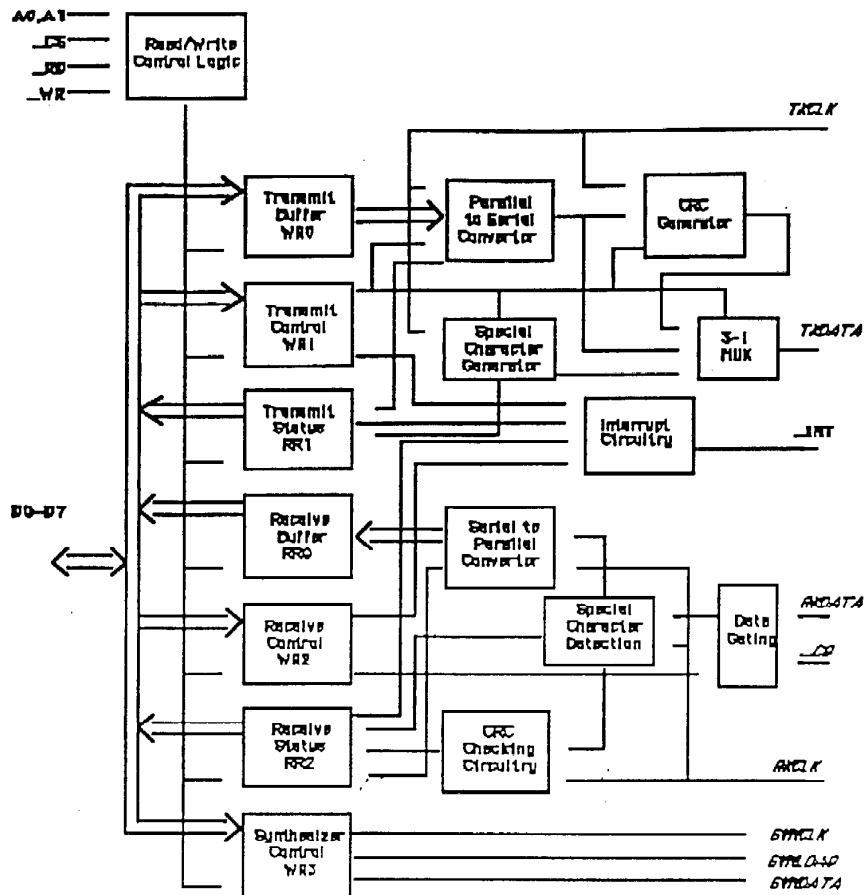

Figure 4 is an expanded diagram showing the details of the microprocessor bus interface, the HDLC Receive Block, and the HDLC Transmit Block. It shows the various registers accessible by the parallel interface and how they interact with the HDLC controller and radio hardware.

Figure 3 - RDA Series Block Diagram

Notes: BOLD=interface signal, /ITALIC=internal signal

Figure 4 - RDA Series Bus Interface Diagram

### 3.1 Transmitter Operation

The first step of the transmit process is to bring the radio out of the Standby mode by raising the STANDBY line high, while the TX/RX line is held low (if this has not already been done). After a power on delay, the transmitter frequency can be programmed by writing a sequence of bytes to the Synthesizer Control Register for the RDA radio. After the transmit frequency has settled, transmission is initiated by raising the TX/RX line. This line will turn off the receiver section while enabling the transmitter output amplifiers. After a transmitter turn on delay, the radio will be ready to send valid data.

The RDA radio includes a full HDLC controller that is controlled through a parallel bus interface. There are 4 write registers and 3 read registers on the RDA which are used to set up the radio and to send and receive data packets. The HDLC protocol involves sending packets which include an opening FLAG, a number of DATA bytes, a 16 bit CRC (Cycle Redundancy Check), and a closing FLAG. The FLAG character is a 01111110, and is differentiated from data by a feature called zero insertion and deletion which inserts a zero after any block of 5 successive 1's in the DATA or CRC blocks. As the transmitter is turning on, an ABORT character 11111111 can be sent repeatedly until it is possible to send a packet. The ABORT character can also be sent between packet transmissions.

Once the RDA radio is ready to transmit valid data, an HDLC packet can be transmitted by appropriately sending a FLAG, DATA bytes, a CRC, and a closing FLAG. The RDA radio can be operated in either interrupt or polled modes, and it must be serviced every byte period while transmitting to tell it to send a control character or to provide a new data byte. The 16 bit CRC is automatically generated by the RDA radio and the RDA radio also handles the zero insertion and deletion features. The FLAG and ABORT characters are generated by the RDA and sent by setting bits in control registers so that they do not undergo zero insertion.

The HDLC Transmitter on the RDA produces a serial data stream which then drives the spread spectrum section of the radio. This serial data stream is scrambled to ensure even spectral content of the output in the event that all 1's or all 0's are transmitted. The scrambled data is modulated in the spreading section by a pseudo-random noise sequence. This signal is conditioned further for spectral shape in the spectral conditioner. The resultant signal is modulated by the RF source to produce the final transmit signal. Finally, the signal is amplified to the desired output power.

### 3.2 Receiver Operation

The first step of the receive process is to bring the radio out of Standby mode by raising the STANDBY line high while the TX/RX line is held low (if this has not already been done). After a power on delay, the receiver frequency can be programmed by writing a sequence of bytes to the Synthesizer Control Register on the RDA radio. After the receive frequency has settled, valid data can be received by the RDA radio.

Signals enter the radio via the antenna connector. A front-end band pass filter rejects signals outside the 902-928MHz band. A low noise amplifier (LNA) performs the first stage of signal amplification. After passing through the LNA, the signal enters the RF Downconverter for translation to an Intermediate Frequency (IF). The IF filter then rejects interference present at frequencies other than the selected frequency channel. Next, the demodulator converts the signal into a form presentable to the de-spreader. The de-spreader, the core of the spread spectrum receiver, correlates the incoming signal and extracts the transmitted clock and data. Finally, the descrambler reverses the scrambling performed by the transmitter, resulting in a serial data stream.

The RDA radios' HDLC controller operates on the recovered serial data stream. Special FLAG and ABORT characters are detected and reported through status bits and interrupts. Any zeros that the transmitter has inserted in the data are removed, and the received packet CRC is computed. If any errors were detected in the received data, a status bit is set. Finally, the received data is converted from serial to parallel form and can be read over the bus interface. The radio can be operated in either interrupt or polled modes, and it must be serviced every byte period while receiving a packet to read the latest data byte or status indication.

### 3.3 Synthesizer

Common to both the receiver and transmitter is the frequency synthesizer. It generates the RF frequencies needed for both the transmitter and the RF Downconverter in the receiver chain.

In the transmit mode, the synthesizer is programmed to the exact transmit frequency, between 902 and 928 MHz. In the receive mode, however, the synthesizer is programmed to a higher frequency for high side injection into the RF Downconverter. This method of tuning allows the radio to receive a packet in one channel, then transmit the following packet in a different channel if desired. This feature is particularly useful for repeaters.

The synthesizer can tune over a wide range of frequencies. This must be kept in mind when in operation. If the synthesizer is programmed to a frequency outside the 902-928MHz band while the transmitter is enabled, the radio will be in violation of FCC regulations.

### 3.4 TX/RX Line

The TX/RX line controls the pre-driver stages in the power amplifier and the supply current to the receiver. Since the output amplifier is a Class C (unbiased) type, it draws negligible supply current in the absence of RF power. This has the advantage that there is no need for a high-current, high-power switch to control the output. In battery-operated applications, the high-current supply (VBAT) can be connected directly to the battery.

### 3.5 STANDBY

The STANDBY switch controls the power supply to most of the radio. When the radio comes out of Standby mode, the supply voltages must settle before the radio can be used. Radio timing is fully described in section 4.

### 3.6 RSSI

The radio provides a Received Signal Strength Indicator (RSSI) derived from the high gain amplifiers in the radio IF section. This indicator measures RF power present in the channel being received. Its voltage varies from approximately 1V to 4V for input signal levels between -100dBm and -30dBm respectively. The RSSI does not indicate a valid spread spectrum code or a low bit error rate. If, for instance, a strong level is indicated on the RSSI, but the carrier detect output is still inactive, then there is interference present in the channel. This feature can be useful for channel selection. This line's output impedance is ~100KΩ.

## 4 Operation

This section describes the procedures one must follow in order to establish communication between two RDA series radios. Section 4.1 *Overview* briefly covers the major steps necessary to prepare the radio for communication. Section 4.2 *Parallel Interface* presents registers descriptions and timing diagrams that explain how to operate the parallel interface/HDLC controller. Section 4.3 *Radio Control* provides procedures and timing diagrams for placing the radio into each of its fundamental modes: Transmit, Receive and Standby. The final operation section, section 4.4 *Data Interface Timing*, details procedures involved in communicating between two radios.

### 4.1 Overview

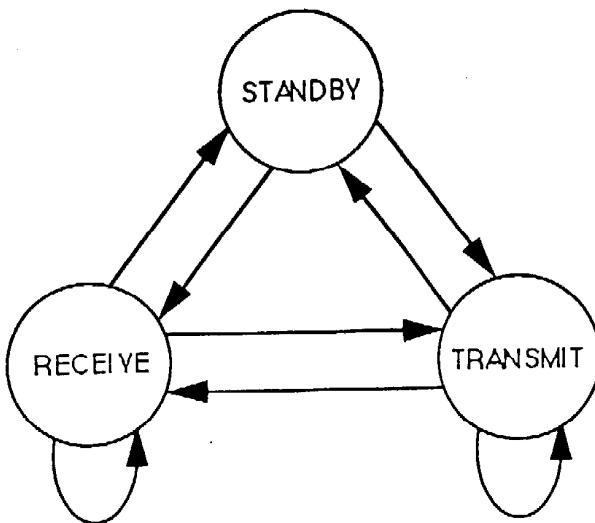

The radio is always in one of three modes: Transmit, Receive or Standby. In Transmit and Receive modes, the radio is transmitting/receiving data on the channel selected during setup. In Standby mode, the radio consumes minimal power and does not perform any RF operation.

Timing is critical when transitioning from one mode to another. In addition, the synthesizer must be reloaded when changing the channel or altering the Transmit/Receive mode. As an example, to bring the radio from Standby to Transmit mode, requires the following steps:

- Set the TX/RX line low.

- Raise the STANDBY line high.

- Wait for the hardware to power-up.

- Program the synthesizer to transmit at the desired frequency.

- Wait for the synthesizer to settle.

- Raise the TX/RX line high to activate the transmitter.

- Wait for the transmitter to reach full power.

- Transmit data packets using the parallel interface to the HDLC controller.

### 4.2 Parallel Interface Overview

This section describes the steps necessary to send and receive data packets using the parallel interface of the RDA radios. The parallel interface consists of 4 write only registers, 3 read only registers, an interrupt line, a TX/RX line, and a STANDBY line. The registers are accessed as follows:

| CS | WR | RD | A1 | A0 | Action                             |

|----|----|----|----|----|------------------------------------|

| 0  | 0  | 1  | 0  | 0  | Write to WR0 (Transmit Buffer)     |

| 0  | 0  | 1  | 0  | 1  | Write to WR1 (Transmit Control)    |

| 0  | 0  | 1  | 1  | 0  | Write to WR2 (Receive Control)     |

| 0  | 0  | 1  | 1  | 1  | Write to WR3 (Synthesizer Control) |

| 0  | 1  | 0  | 0  | 0  | Read RR0 (Receive Buffer)          |

| 0  | 1  | 0  | 0  | 1  | Read RR1 (Transmit Status)         |

| 0  | 1  | 0  | 1  | 0  | Read RR2 (Receive Status)          |

The TX/RX line is used to place the RDA radio into the Transmit mode when it is set high, and places the radio into Receive mode when it is set low. The STANDBY line is used to place the entire RDA radio in a shutdown/reset mode when it is set low. The interrupt line of the RDA parallel interface is optional, and can be used in interrupt driven systems. As an alternative, the RDA radios fully support polled mode operation.

### Transmit Mode

When sending an HDLC packet using the RDA radio, there are three parallel interface registers that are used: the Transmit Buffer (WR0), the Transmit Control Register (WR1), and the Transmit Status Register (RR1). The Transmit Control Register (WR1) determines what character will be sent by the RDA radio next. The options are an ABORT, FLAG, or WAKEUP special character, as well as a data byte which is stored in the Transmit Buffer (WR0) and an internally generated two byte CRC. The ABORT, FLAG, WAKEUP, and CRC characters can each be simply generated and sent by setting the appropriate bits in the Transmit Control Register (WR1).

) The Transmit Character Request status bit, in the Transmit Status Register (RR1 Bit1) is set as soon as the command to send the last character has been accepted by the RDA radio. At this point, the RDA radio is ready to accept a new command which will identify the next character to send, since the previous character has been loaded and is being shifted out of the radio. The Transmit Character Request bit can be used to generate an interrupt signal from the RDA radio when transmitting. It is qualified by a number of bits in the Transmit Control Register (WR1) when generating an interrupt. These permit the interrupt to be shut off while repeatedly sending special characters such as ABORT, FLAG or WAKEUP. This feature allows a special character to be auto-repeated without triggering Transmit Character Requests which would require repeated intervention by the host processor. The Transmit Character Request bit is cleared by writing to the Transmit Control Register (WR1) or the Transmit Buffer (WR0).

A user data byte is sent by writing to the Transmit Control Register (WR1) to configure it to send data, and loading the data byte into the Transmit Buffer (WR0). The first data byte of a packet should be pre-loaded into the Transmit Buffer (WR0) prior to setting up the Transmit Control Register (WR1) to send data. Transmission of subsequent bytes is initiated by simply writing to the WR0. The Transmit Buffer (WR0) is single buffered, so that while the previous byte is being shifted out of the radio, a new byte should be loaded into the WR0 register. The Transmit Status Register (RR1) contains status bits which show whether the Transmit Buffer (WR0) is full, whether a new character is being requested (Transmit Character Request), and whether a Transmitter Overrun or Underrun has occurred.

### Receive Mode

When receiving a HDLC data packet using the RDA radio, there are three parallel interface registers that are used: the Receive Control Register (WR2), the Receive Buffer (RR0), and the Receiver Status Register (RR2). The Receive Control Register (WR2) is used to setup the sources of receiver interrupts, and to setup the gating of the received data with the Carrier Detect signal. The Receiver Status Register (RR2) reports the reception of ABORT, FLAG, WAKEUP, DATA and CRC characters. Another bit in the Receiver Status Register (RR2) is cleared when a valid CRC character has been received, and is set when an invalid CRC has been received. Finally, the Receiver Status Register (RR2) contains a bit which indicates whether a receiver overrun has occurred which indicates that the host processor failed to read a data byte before it was overwritten. The RDA radio contains a single level of output data buffering, so the host processor must be able to read received data bytes within a byte period of their detection.

The Receiver Status Register (RR2) is generally read each time a receive interrupt is received to determine the source. The Receive Buffer (RR0) holds the last data byte that has been received by the RDA radio. The Receive Buffer should be read after the Data Ready bit in the Receiver Status Register (RR2) has been set. A number of bits in the Receive Control Register (WR2) are used to mask various receive interrupt sources. The most important of these is Bit2 which is used to mask ABORT interrupts. When a receiver is turning on, the received data will most likely be gated high before valid data is received, and this will appear as a continuous stream of ABORT characters. To avoid continuous ABORT interrupts in the power on stage, this interrupt source should be masked, and the host processor should be interrupted on an opening FLAG which signifies the beginning of a valid data packet.

The following two sections show typical sequences of events for sending and receiving data packets. They utilize the interrupt feature of the RDA radio to trigger actions. If a polled mode of operation is desired as an alternative, the appropriate bits in the Transmit Status Register (RR1) and the Receiver Status Register (RR2) can be continuously monitored by the host processor. Many variations can be made to these typical sequences, and the user is referred to Section 4.3 which lists detailed descriptions for the operation of the various bits in the RDA radio parallel interface.

**Typical Sequence of Events to Send a Data Packet

(Using Interrupts)**

- Take the RDA radio out of Standby by setting STANDBY high, and setting TX/RX low.

- Wait for the RDA radio to power up.

- Program the RDA synthesizer by writing a sequence of bytes to WR3 (described in section 4.3.1).

- Wait for the synthesizer to settle.

- Set the TX/RX line high for Transmit mode.

- Setup the RDA radio to send continuous ABORT characters while it is powering on by setting the appropriate bits in the Transmit Control Register (WR1). The interrupt line of the RDA in Transmit mode is tied to the Transmit Character Request bit in the Transmit Status Register (RR1). When the RDA radio is requesting information on what character to send next, the Transmit Character Request bit is asserted. The Transmit Character request should be disabled for the ABORT character so that interrupts are not generated after each character is sent. Both of these operations can be performed by setting WR1 to "00001000".

- Wait for the transmitter to power up and the receiver to lock up.

- Enable Transmit Character Request interrupts for the ABORT character by writing to WR1. This will generate an interrupt after the next ABORT character is sent. This is done by setting WR1 to "00000000".

- When the next RDA interrupt is received, set up the radio to send a FLAG character and enable Transmit Character Requests for the FLAG character by writing to WR1. This will cause an opening FLAG to be sent as the next character. This is done by setting WR1 to "00000001".

- When the next RDA interrupt is received, load the first data byte into WR0. The radio should immediately be setup to send data by writing a "00000100" to WR1.

- When the next RDA interrupt is received, load the next data byte into WR0. It is not necessary to write to WR1 for each byte in the data packet.

- Continue to send data bytes by loading the next byte into WR0 after each interrupt is received.

- After the last data byte has been sent, and when the next RDA interrupt is received, setup the RDA to send the CRC bytes by writing to WR1. This requires a single write to WR1 to trigger the transmission of two consecutive CRC bytes. This is done by writing "00000011" to WR1.

- When the next RDA interrupt is received, write to WR1 so that the RDA will send the closing FLAG character. This is done by writing "00000001" to WR1.

- Setup the RDA radio to send continuous ABORT characters while it is powering off by setting the appropriate bits in the Transmit Control Register (WR1). The Transmit Character request should be disabled for the ABORT character so that interrupts are not generated after each character is sent. Both of these operations can be performed by setting WR1 to "00001000".

- Set the TX/RX line low to place the radio into receive mode.

- Wait for the transmitter to power down.

- Switch the RDA radio off by setting STANDBY low.

**Typical Sequence of Events to Receive a Data Packet

(Using Interrupts)**

- Take the RDA radio out of Standby by setting STANDBY high, and setting TX/RX low.

- Wait for the RDA radio to power up.

- Program the RDA synthesizer by writing a sequence of bytes to WR3 (described in section 4.3.1).

- Wait for the synthesizer to settle.

- Setup the RDA radio to allow interrupts from a FLAG character, and to gate the received data with Carrier Detect by writing to WR2. Gating the received data with the Carrier Detect ensures that random noise will not inadvertently create a FLAG interrupt when no signal is being detected by the RDA radio. These actions are done by writing "01110110" to WR2.

- Upon receiving an interrupt, the RDA radio has received a FLAG character, and a packet should be coming. There will be approximately a 4 byte delay until the first data byte is ready to read. Setup the RDA radio to allow interrupts from FLAG and ABORT characters as well as the DATA byte that is expected. Since a valid data packet is being received, the received data should no longer be gated with Carrier Detect. This is done by writing "00010000" to WR2.

- Upon receiving an interrupt, verify that it is from the first data byte being read by checking the Receiver Status Register (RR2). If the Data Ready Bit is set, then read the data byte from the Receive Buffer (RR0).

- Continue to check the Receiver Status Register (RR2) when receiving interrupts. When data bytes are ready, they can be read from RR0, and eventually when the closing FLAG of the HDLC packet is recognized, the final data byte, and the CRC result will all be ready simultaneously.

- Verify that the CRC result in the Receiver Status Register (RR2) is correct.

- The packet has been received, and the RDA should now be setup to interrupt only on a new opening FLAG character, and the received data should be gated with carrier detect. This is done by writing "01110110" to WR2.

#### 4.2.1 Register Descriptions

**Transmit Buffer (WR0)**

(Line Settings: A1=0, A0=0; CS=0, RD=1, WR=0)

This register contains the next data byte to transmit. It is cleared when STANDBY=0 or TX/RX=0

**Transmit Control (WR1)**

(A1=0, A0=1; CS=0, RD=1, WR=0)

This register contains the HDLC transmitter control bits. These bits are cleared when STANDBY=0 or TX/RX=0.

Bit0-Bit2 determine the next character the radio will send. There are five possible selections for transmission: ABORT, FLAG, WAKEUP, DATA or CRC. The ABORT, FLAG and WAKEUP characters as well as DATA (the contents of the Transmit Buffer), are all a single byte long. The internally calculated CRC is two bytes long. A single write to the Transmit Control Register sends both CRC bytes. The following table lists shows the character to be sent next based on Bit0-Bit2 settings.

| BIT2 | BIT1 | BIT0 | Next Character to Be Sent           |

|------|------|------|-------------------------------------|

| 0    | 0    | 0    | ABORT (1111111)                     |

| 0    | 0    | 1    | FLAG (01111110)                     |

| 0    | 1    | 0    | WAKEUP (01111111)                   |

| 0    | 1    | 1    | CRC (internally calculated 2 bytes) |

| 1    | 0    | 0    | DATA (Transmit Buffer contents)     |

| 1    | 0    | 1    | ABORT (11111111)                    |

| 1    | 1    | 0    | ABORT (11111111)                    |

| 1    | 1    | 1    | ABORT (11111111)                    |

Bit3-Bit5 are the Transmit Character Request (TCR) Mask bits. These bits determine whether a new character will be requested after sending an ABORT, FLAG or WAKEUP character. These bits allow the user to send one of these characters continuously without receiving transmit character requests or interrupts after each character.

| BIT3 | Description                          |

|------|--------------------------------------|

| 0    | TCR is produced when sending ABORTS  |

| 1    | TCR is masked when sending ABORTS    |

| BIT4 | Description                          |

| 0    | TCR is produced when sending FLAGS   |

| 1    | TCR is masked when sending FLAGS     |

| BIT5 | Description                          |

| 0    | TCR is produced when sending WAKEUPS |

| 1    | TCR is masked when sending WAKEUPS   |

Bit6 is the Transmitter Interrupt Mask. Setting this bit to a value of "1" will mask all transmit interrupts.

Bit7 of the Transmit Control Register must be set to "0" for the radio to pass FCC regulations.

**Receive Control (WR2)**

(A1=1, A0=0; CS=0, RD=1, WR=0)

The Receive Control Register contains the HDLC Receiver control bits. These bits are cleared when STANDBY=0 or TX/RX=1.

Bit0 must be set to "0" for proper operation.

Bit1-Bit5 set up masks for the possible receive interrupts: DATA ready, ABORT, FLAG, WAKEUP, and CRC.

| BIT1 | Description                                                         |

|------|---------------------------------------------------------------------|

| 0    | Received DATA Byte causes interrupt.                                |

| 1    | Received DATA Byte Interrupt masked.                                |

| BIT2 | Description                                                         |

| 0    | Received ABORT causes interrupt.                                    |

| 1    | Received ABORT Interrupt masked.                                    |

| BIT3 | Description                                                         |

| 0    | Received FLAG causes interrupt.                                     |

| 1    | Received FLAG Interrupt masked.                                     |

| BIT4 | Description                                                         |

| 0    | Received WAKEUP causes interrupt.                                   |

| 1    | Received WAKEUP Interrupt masked.                                   |

| BIT5 | Description                                                         |

| 0    | CRC Received causes interrupt.                                      |

| 1    | CRC Received Interrupt masked.                                      |

| BIT6 | Description                                                         |

| 0    | Received DATA passes directly into HDLC Receiver Block.             |

| 1    | Received DATA is gated high whenever valid carrier is not detected. |

When the receiver is on and attempting to receive a packet, it is recommended that Bit6 be set to "1". In this case, if there is no valid input, the HDLC controller will see a constant high level on the received data line which will be interpreted as an ABORT character. If Bit6 were set to "0", the HDLC controller could interpret random noise as a false opening FLAG.

Once a valid opening FLAG is received, Bit6 should be set to "0" to fully utilize the radio's sensitivity and range. At this point, it is known that the data being received is not random, and no longer requires gating by the carrier detect signal.

Bit7 must be set to "0" for proper operation.

**Synthesizer Control (WR3)**

(A1=1, A0=1; CS=0, RD=1, WR=0)

This register contains the three bits that control the synthesizer. These bits are cleared when STANDBY=0.

Bit0 drives the Synthesizer Clock line (SYNCLK).

Bit1 drives the Synthesizer Data line (SYNCDATA).

Bit2 drives the Synthesizer Load line (SYNLD).

See Section 4.3.1 for proper programming of synthesizer control lines.

**Transmitter Status (RR1)**

(A1=0, A0=1; CS=0, RD=0, WR=1)

This register contains all of the HDLC transmitter bits. It is cleared when STANDBY=0 or TX/RX=1.

Bit0 is the Transmit Buffer Full bit. When this bit is set to "1", the Transmit Buffer (WR0) is full, and writing to it again will overwrite its present contents.

Bit1 is the Transmit Character Request bit. This bit is set to "1" when the HDLC Transmitter is requesting either a new data byte or a command to send a new special character. This bit is cleared by writing to the Transmit Buffer (WR0) or the Transmit Control Register (WR1).

Bit2 is the Transmitter Overrun bit. This bit is set to "1" if the Transmit Buffer (WR0) was written to while it was full. This bit is cleared when this register is read.

Bit3 is the Transmitter Underrun bit. This bit is set to "1" if the Transmit Buffer (WR0) was not written to in time while sending a data packet. This error condition results in an ABORT character being sent which effectively terminates the packet. This status bit is cleared when this register is read.

**Receive Buffer (RR0)**

(A1=0, A0=0; CS=0, RD=0, WR=1)

This register contains the last data byte received. It is cleared when STANDBY=0 or TX/RX=1.

**Receiver Status (RR2)**

(A1=1, A0=0; CS=0, RD=0, WR=1)

This register contains the receiver status bits for the HDLC controller. These bits are cleared when STANDBY=0 or TX/RX=1.

Bit0 is the CRC Result bit. This bit is set to a "0" when a received data packet's CRC is checked and is good. This bit is set to a "1" when the CRC is checked and is invalid.

Bit1 is the CRC Received bit. This bit is set to a "1" when the CRC result is calculated and stored in Bit0. The CRC Received bit is set on a closing FLAG of a data packet in which at least one data byte and two CRC bytes have been read. This bit is cleared when this register is read.

Bit2-Bit4 are the special Character Detection bits. These bits are set whenever a specific special character has been detected and are cleared when this register is read. Bit2 corresponds to an ABORT character, Bit3 corresponds to a FLAG character, and Bit4 corresponds to a WAKEUP character.

Bit5 is the Data Ready bit. This bit is set when a new data word is written into the Receive Buffer (RR0) and is cleared when the Receive Buffer (RR0) or the Receiver Status Register (RR2) is read.

Bit6 is the Receiver Overrun bit. This bit is set when a new received data byte is ready before the previous data byte in the Receive Buffer (RR0) has been read. This is an error condition because a data byte has been lost.

#### 4.2.2 Bus Interface Timing Diagrams

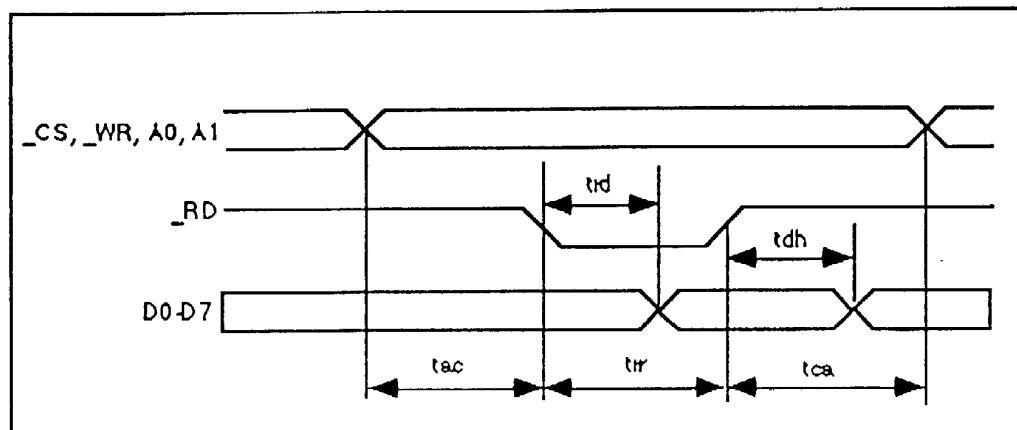

Figure 5 shows the read operation timing diagram. The referenced time constants are:

| Symbol | Time  | Description |

|--------|-------|-------------|

| tac    | 50ns  | MIN         |

| trr    | 100ns | MIN         |

| tca    | 50ns  | MIN         |

| trd    | 35ns  | MAX         |

| tdh    | 5ns   | MIN         |

Figure 5 - Read Timing Diagram

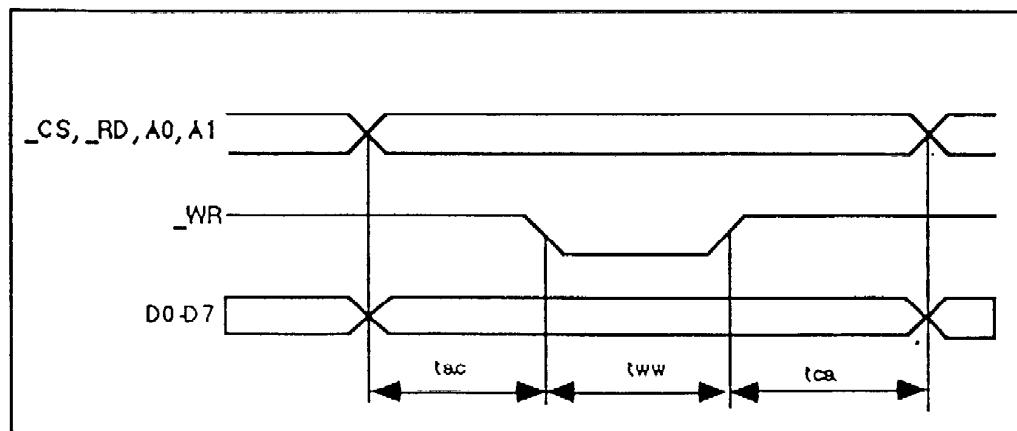

Figure 6 shows the write operation timing diagram. Referenced time constants are:

| Symbol | Time  | Description |

|--------|-------|-------------|

| tac    | 50ns  | MIN         |

| trr    | 100ns | MIN         |

| tca    | 50ns  | MIN         |

Figure 6 - Write Timing Diagram

#### 4.3 Radio Control

This section describes the process for selecting the radio's mode and channel. The *Frequency Programming* section details how control codes are loaded in the Synthesizer Control Register. The sections *Receive Mode*, *Transmit Mode*, and *Standby Mode* each outline the steps necessary to enter that mode from each of the other modes.

Figure 7 - Radio Modes

##### 4.3.1 Frequency Programming

Before the radio can either transmit or receive, the synthesizer must be set to an operating frequency. Table 1 shows the RDA-100's seven frequency channels and their internal representation by the radio. Its four non-overlapping channels are identified by asterisks. The RDA2's three non-overlapping channels are identified by asterisks in Table 2.

The synthesizer is shared by the transmitter and receiver (see Figure 1) and must be reprogrammed whenever changing mode or switching channel.

As shown in Tables 1 and 2, the programming information for the synthesizer consists of a 16 bit word and a 19 bit word, referred to as the Reference Divider Word and RF Divider Word respectively. Once a word has been input into the shift register, it must be loaded into the Synthesizer Control Register before the next word can be shifted in. The synthesizer uses the control bit (C) to differentiate between the Reference Divider Word(1) and the RF Divider Word(0). Tables 1 and 2 describe the bit pattern corresponding to each transmit and receive frequency available.